- HOME

- モデルベースデザインで FPGA 開発はどう変わる? ZCU106 を用いた実例で理解する MBD の価値

設計 モデルベース開発ソリューション

モデルベースデザインで FPGA 開発はどう変わる?

ZCU106 を用いた実例で理解する MBD の価値

FPGA や組込み開発の現場では、仕様の複雑化、開発期間短縮、属人化など、従来手法の課題がより鮮明になっています。その中で注目されているのが モデルベースデザイン(MBD) です。

本記事では、東京エレクトロンデバイス(以下、TED)が 「ZCU106」を用いて Simulink による「MBD」を実際に適用した事例をもとに、開発プロセスと得られた効果を紹介します。

ZCU106の開発事例

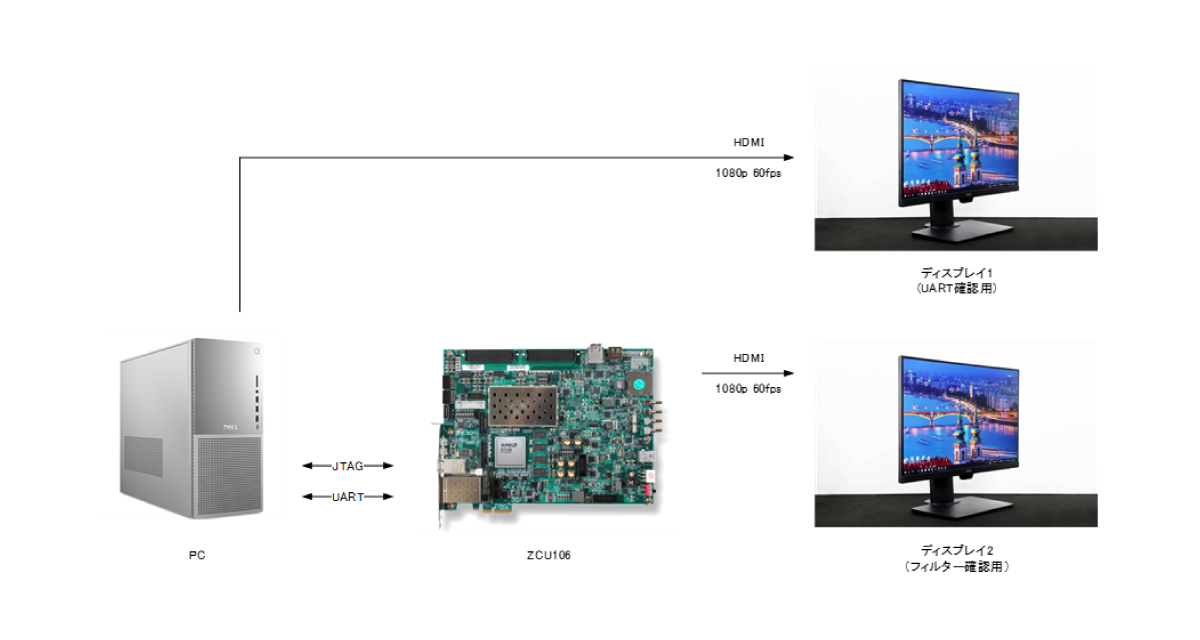

本開発では次の構成を実現することを目標としました。

目標

- HDMI 入力映像を ZCU106 で受信

- FPGA 内で 赤成分 (R) を 0.25 に減衰 する RGB フィルタを実行

- HDMI 出力でフィルタ効果を確認

この一連の流れを「Simulink でのモデル設計」>「FPGA 実装ファイル生成」>「ハードウェア検証」まで統合して実施しています。

Color Barの動作確認構成全体図

Color Barの動作確認構成全体図

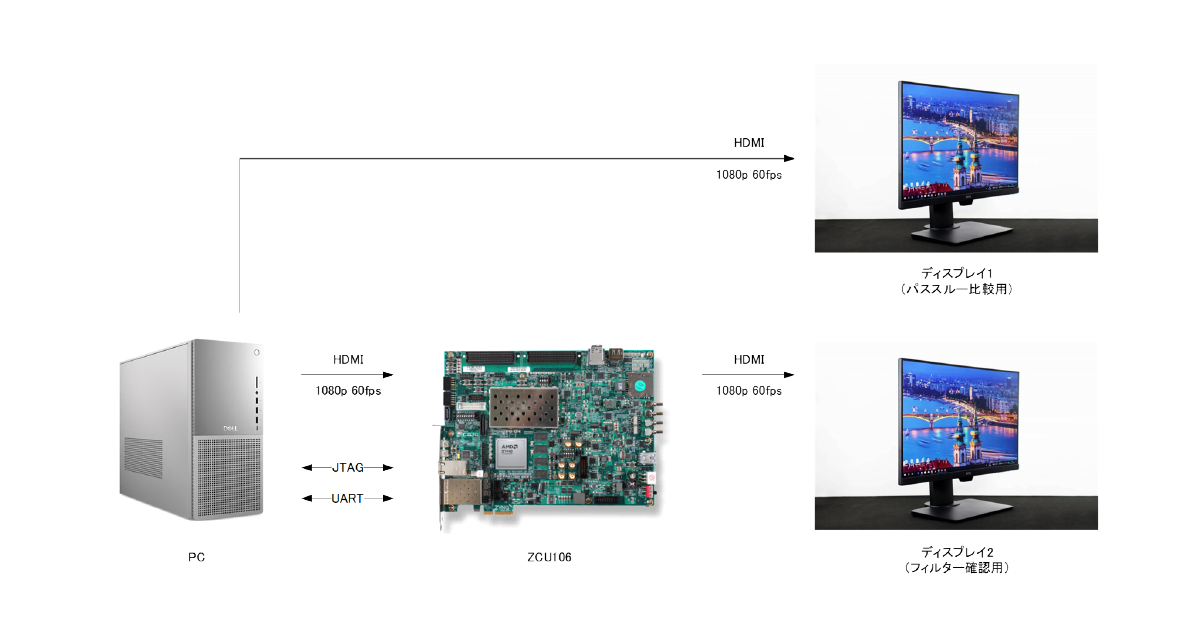

Pass-Throughの動作確認 構成全体図

ZCU106の開発プロセス

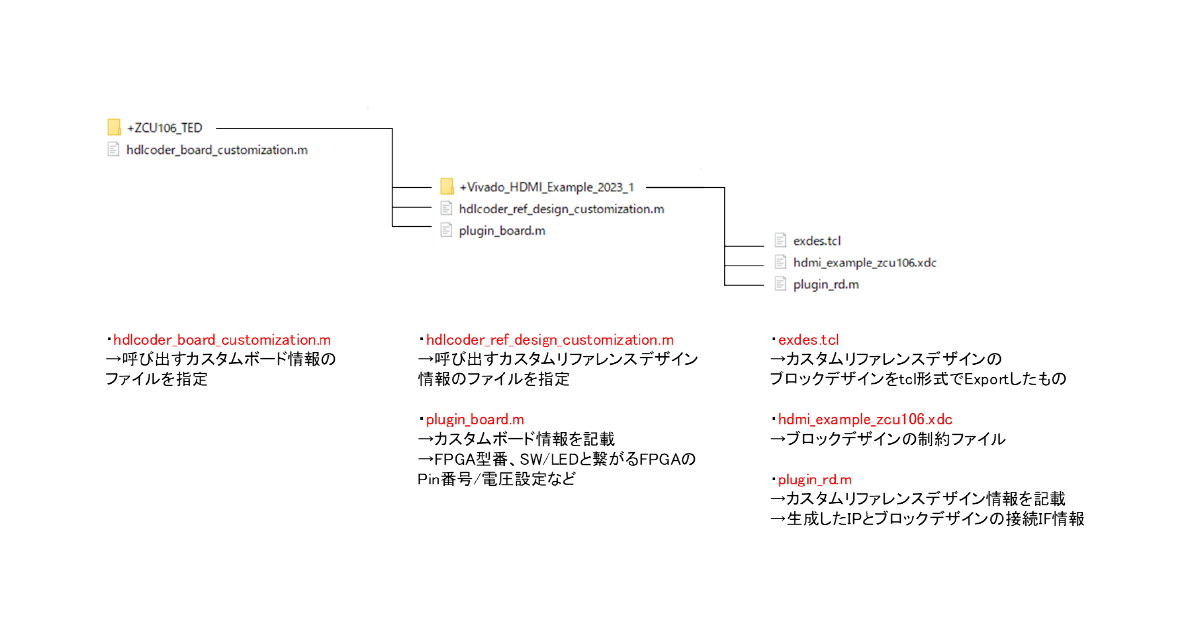

STEP 1:リファレンスデザインの改造

- HDMI Pass-Through Design をベースに、HDMI RX → フィルタ → HDMI TX の流れを実現するための block design へ改造

- AXI4-Stream 接続の一部を削除し、Simulink 生成 IP を挿入可能な構造へ変更

- 変更後 block design を tcl 形式でエクスポート

カスタムの基板・ブロックデザインをSimulinkへ適応させるのに必要なファイル一覧

STEP 2:Simulink によるフィルタモデル設計

- R 成分を 0.25 に減衰する RGB フィルタブロックを設計

- 「2Pixel 入力」→「1Pixel 処理」→「2Pixel 出力のデータ構造をモデル化」

- HDL 対応ブロックとシミュレーション用ブロックを整理

STEP 3:Simulink → Vivado への実装生成

- HDL Workflow Advisor を用いて、ターゲットボード設定(ZCU106 + Vivado)

- IP Core 生成

- Vivado プロジェクト生成ビットストリーム生成

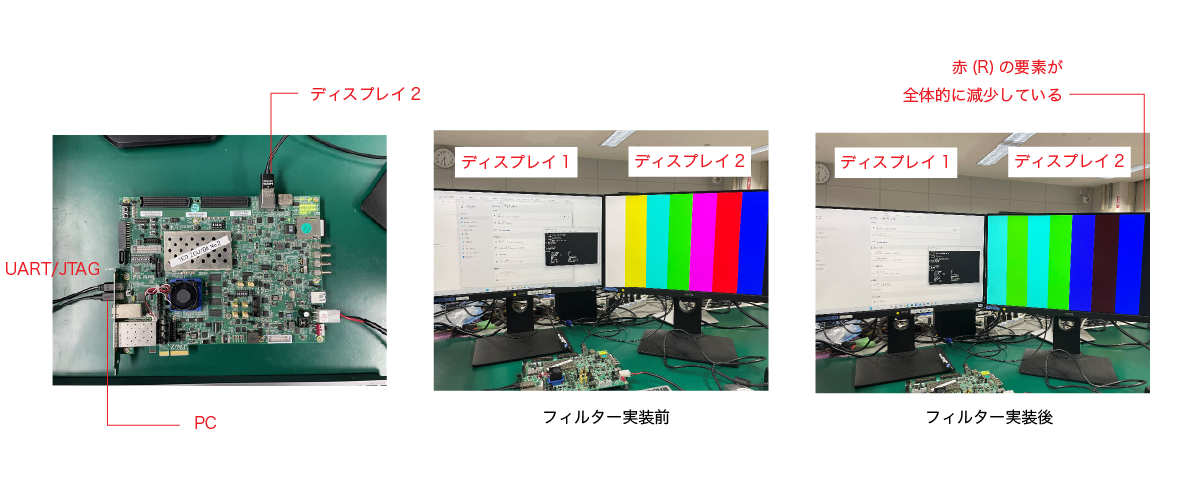

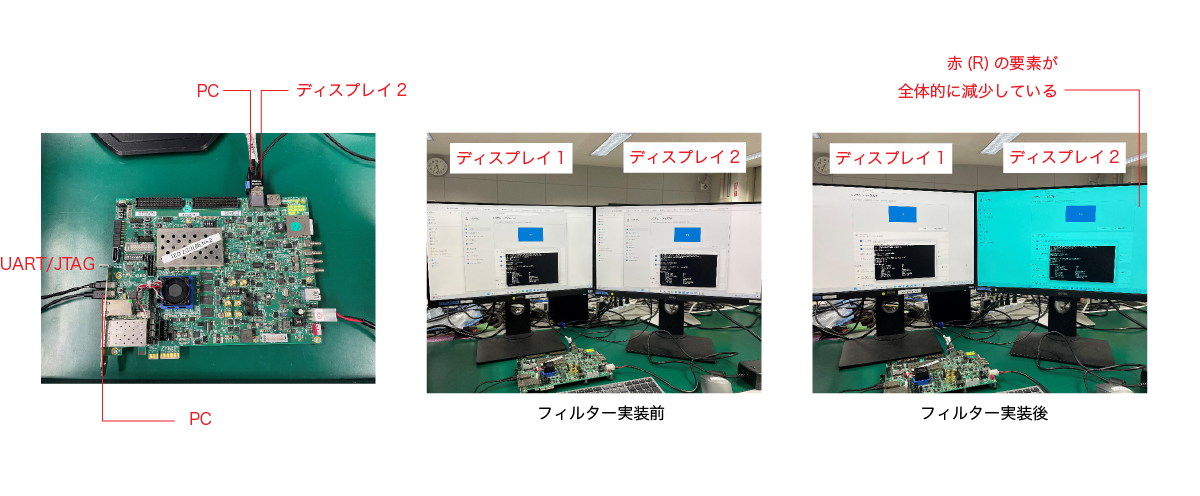

STEP 4:ZCU106 での動作確認

- Color Bar / Pass-Through との差分を HDMI 出力で比較

- 赤成分(R)が確実に減衰していることを実機で確認

フィルター実装前のPass-Through Exampleと実装後のデザインの動作結果比較

フィルター実装前のPass-Through Exampleと実装後のデザインの動作結果比較

※PCは画面複製モードで出力

MBD のメリット・ TED が支援できるポイント

MBD を活用することで、設計〜実装〜検証までを統合的に処理でき、FPGA 開発にて大きな効果を得られます。

一方、FPGA には基板固有構造やインターフェース設計など、MBD と組み合わせることでより効率化できる領域も存在します。

以下では、MBD のメリットと TED が支援できるポイントを整理します。

メリット1:自社オリジナル基板への展開性の向上

Simulink には、基板固有情報(I/O、クロック、IP 構成など)を設定ファイルとして渡すことができ、ZCU106 以外の自社基板でも同一ワークフローを展開できます。

MBD の価値

- block design を tcl 化し、異なる基板でも再利用可能

- 設計フローの共通化により開発効率が大幅向上

FPGA 実装で必要となる前提作業

- 基板固有インターフェースの準備

- Vivado block design の調整

TEDの支援

- 基板別インターフェース設計の代行・支援

- Simulink 連携用設定ファイル(tcl / JSON など)作成支援

メリット2:モデルと実装の整合性向上によるデバッグ削減

Simulink 生成 IP が Vivado block design に意図した位置へ正しく挿入され、モデルと実機で動作が一致したことを確認。これによりデバッグ工数が大幅に減少します。

MBDの価値

- RTL/FPGA 実装とのズレが発生しにくい

- 実機でモデルと同じ動作を確認しやすい

活用上のポイント(FPGA 全般)

- AXI4-Stream などのデータフロー理解

- 高速映像 IF の正しい接続

TEDの支援

- HDMI / AXI4-Stream の設計経験に基づく IP 配置支援

- デバッグしやすい block design 構造の設計支援

メリット3:既存リファレンスデザインの効果的な再利用

MBDの価値

- 既存のリファレンスを活かしつつ、自社機能へ柔軟に拡張可能

- Simulink ↔ Vivadoの自動化により手戻りを排除

TEDの支援

- HDMI 系デザイン改造の豊富な実績

- 自社用途へのカスタム拡張ガイド

- tcl 化・ワークフロー統合のサポート

まとめ

今回の ZCU106 を用いた実践を通じて、MBD の効果として

- 設計と実装が一致する安心感

- ワークフロー一貫化による開発効率化

- 自社基板への展開による技術資産化

といった大きな成果が得られました。

FPGA 開発に MBD を導入することは、単なる効率化ではなく“開発プロセスそのものをアップデートすること” に他なりません。

TEDでは、

- 自社基板で MBD を使ってみたい

- Simulink と Vivado の連携を相談したい

- リファレンスデザインを改造して効率化したい

- MBD 導入のロードマップを作りたい

といったご相談を多くいただいています。貴社プロジェクトに最適な MBD 活用方法をご提案いたしますので、ぜひお気軽にお問い合わせください。