製品・サービス

FPGAを用いたMIPIインタフェース開発

MIPIのロジック開発から基板製造まで

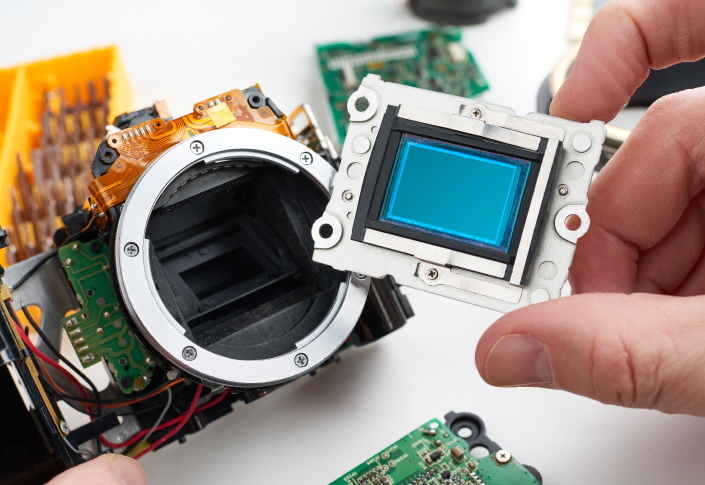

近年、イメージセンサの需要は高まる一方で、MIPIインタフェースの開発は必須事項となりつつあります。東京エレクトロンデバイスは、Lattice社の国内正規代理店としてMIPI関連製品を扱うほか、設計・受託サービスで蓄積したノウハウを基に、お客様が抱えるMIPIに対する課題も解決いたします。

MIPIとは

イメージセンサのインタフェース規格

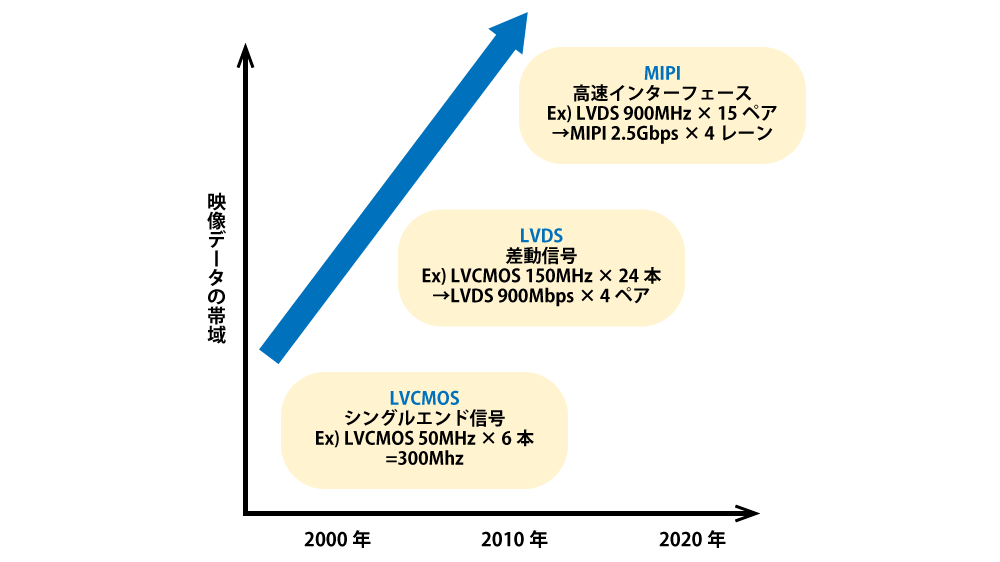

近年、デジタルカメラ、車載カメラ、産業用マシンビジョンなど幅広い用途でイメージセンサの需要が今まで以上に拡大しています。それにともない、映像システムへの要求仕様も時代を追うごとに高性能化が進んでおります。

【例】

・色深度:RGB 8bit → 12bit

・解像度:FullHD 1920×1080 → 4K 3840×2160

・フレームレート:30fps → 60fps

また映像データを転送するためのインタフェースのトレンドも、イメージセンサの高性能化にあわせて変化しています。

・伝送ライン本数を削減

・伝送ライン1本あたりの伝送帯域の高速化

・差動信号採用による低電圧化、消費電力の低減

最近のイメージセンサでは、これらの要求を満たすことのできる映像用高速インタフェース規格、MIPI が広く採用されています。

MIPI 設計時の課題

イメージセンサのインタフェース用途として一般的な規格となった MIPIですが、実際の設計の現場においては、依然として以下のような課題に直面することが多くあります。

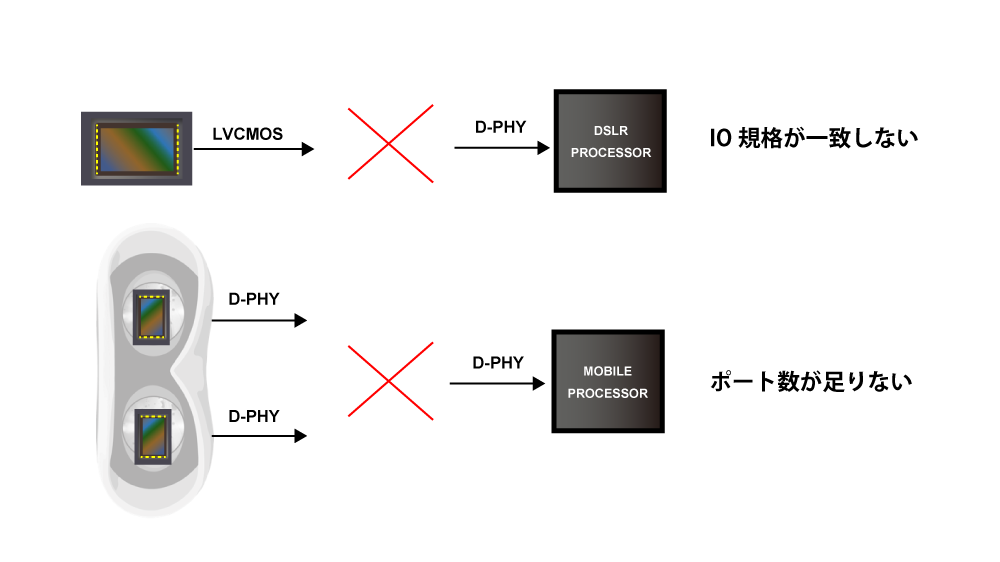

課題1 インタフェースの不一致

イメージセンサとその後段のプロセッサや画像処理デバイスの間で、IO規格が一致しないため直結できない。またはポート数が足りない。

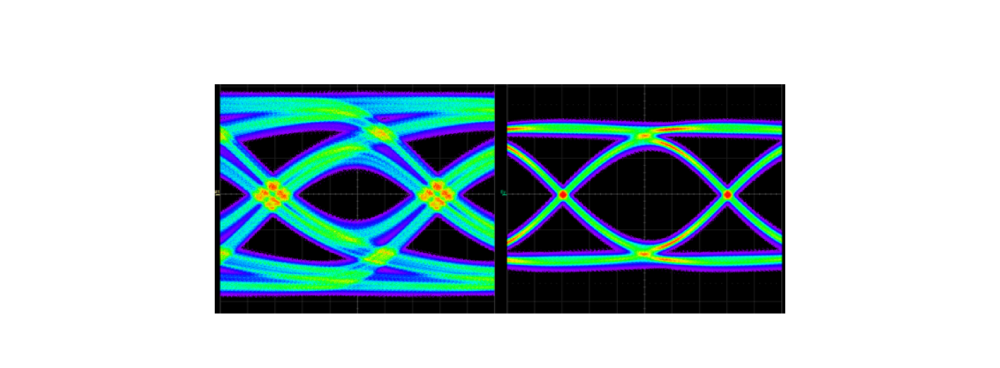

課題2 基板設計の難易度

数百Mbps以上の高速伝送が必要となり、かつ基板上すべてのレーンが等配線遅延になることが求められ、基板設計が難しい。

課題3 技術の世代交代が早い

高機能化や多様化による映像技術の世代交代が早い。インタフェースブリッジASSPは、比較的容易に適用可能であるが、スペックが固定されるため映像技術の進歩にあわせた機能拡張に対応することが難しい。特に旧世代製品については長期供給されないケースが多い、購入数量条件が厳しい、といったデメリットがある。

FPGAによる課題解決

ASSPのデメリットである機能拡張性や入手性の問題を解決するためには、FPGAの活用がおすすめです。

・MIPIインタフェース回路のほかに、ユーザーデザインの追加が可能

・画像処理を行うメインチップの負荷を分散したり、独自の映像処理回路を実装して、機能の差別化を図ることが可能

・イメージセンサが変更になってもブリッジチップの変更が不要であるため基板の改版リスクが小さい

・採用中のFPGAが終息となった場合であっても、他のFPGAへの移行が比較的容易

課題解決可能なFPGA

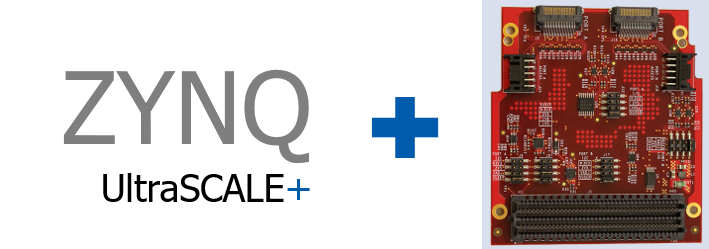

MIPIインタフェースに加えてプロセッサ、画像処理などの 機能実装を検討する場合

・16nm FinFET+ プログラマブルロジック

・クワッド Arm Cortex-A53、Arm Mali-400MP2、H.264/H.265

ビデオコーデック搭載のラインアップ有

・さまざまな高速シリアルインタフェース規格をサポート

・MIPI データレートは1レーンあたり最大2.5Gbps

ASSPに近いイメージで手軽にMIPIインタフェースのブリッジを行いたい場合

・Lattice Nexus Platform (28nm FD-SOIプロセス) 採用により

消費電力、ソフトエラーレートを大幅に低減

・2.5 Gbps ハードウェア MIPI D-PHY、PCI Express Gen2 を

はじめ、DDR3メモリインタフェース、差動I/Oなどのさまざまな

インタフェースをサポート

・最小で3.7×4.1mmの小型パッケージを提供

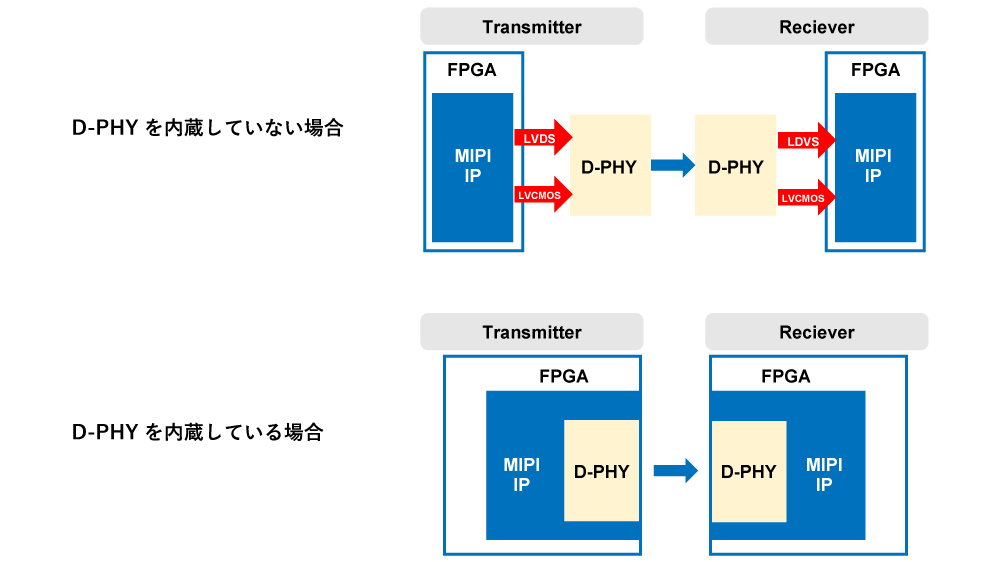

D-PHY内蔵FPGA

MIPI D-PHYは差動の高速モードとLVCMOS 1.2Vの低速モードがあるため、基本的には専用のPHYを使用する必要がありますが、近年のFPGAはD-PHYを内蔵できるデバイスが増えております。ご紹介したZynq UltraScale+ MPSoCとCrossLinkは双方D-PHYを内蔵できるデバイスとなります。

MIPIの開発事例

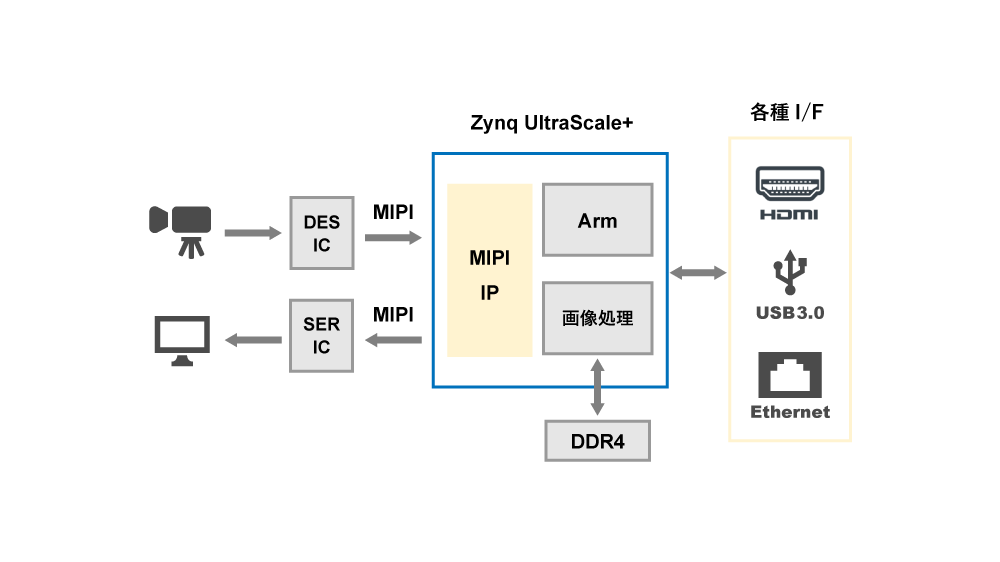

事例1 Zynq UltraScale+ MPSoC用いた事例

Zynq UltraScale+MPSoCを活用した事例です。ベンダー提供のD-PHY内蔵MIPI IPを活用して、シリアル通信IC(SER/DES)との接続やカメラからの映像をFPGAに入力・画像処理を行い、外部インターフェースへ転送するデータの流れになります。

(FPGA入力時のMIPI伝送レートはMAX2.4Gbps x 4lane)

FPGAを使用するメリットとしては、内部信号を観測できるため、パケットが正しく取得できているか確認が可能です。また、テストパターンのジェネレータやチェッカーをFPGA内にロジックとして構築でき、HDMIなどのインターフェースを用意することで、画像確認を行いながら評価可能です。

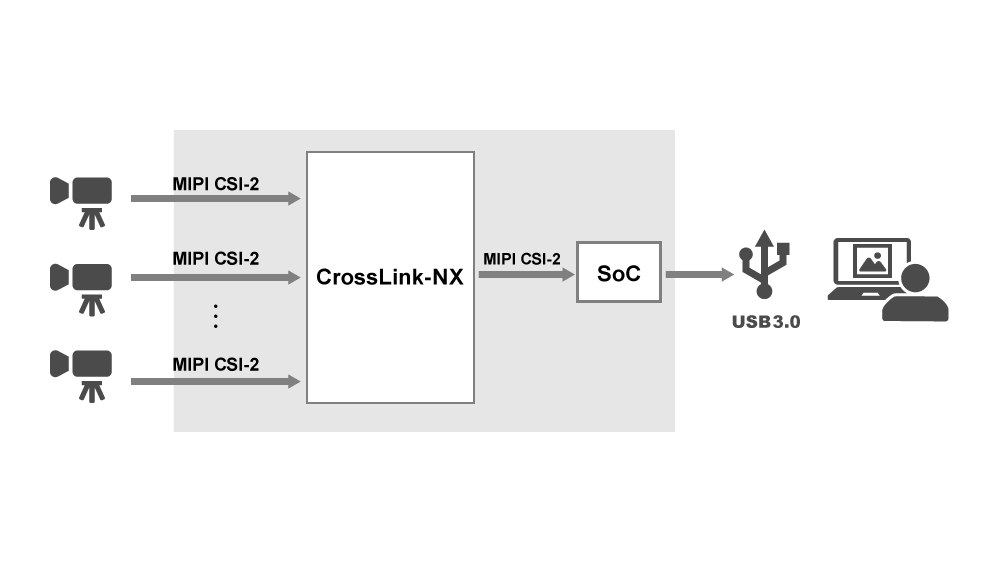

事例2 CrossLink用いた事例

複数カメラ画像をPCへ取り込む変換基板の事例です。単体カメラからMIPI CSI-2で映像を受け取り、PCへデータ転送などは昨今のマイコン・SoCだと容易に実現できますが、複数カメラ入力を束ねることはなかなか容易ではありません。

CrossLink-NXを活用することで、複数のMIPI CSI-2入力データを結合し、拡張した映像をMIPI CSI-2で出力が可能です。

デザインサービスの活用

ロジック開発から基板製造まで設計負荷低減

画像システムの開発に必要な技術は多岐にわたるため、全ての分野を自社でカバーできないケースも考えられます。

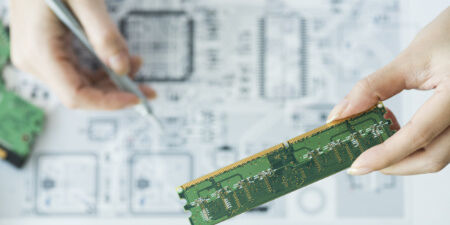

・FPGA論理設計

・ホストプロセッサに搭載されるSoCのファーム開発/デバイスドライバ開発

・評価環境構築

・数百Mbps以上の速度が要求される基板設計・基板製造・部品調達・基板評価(試作・量産)

・他社との差別化機能の実装

このようなお悩みに対して、弊社のデザインサービスでは、下記の通り、FPGAにまつわる知見や経験など、数十年に渡って蓄積したノウハウをバックグラウンドにした、映像システム開発のデザインサービスをご提案することが可能です。

・ザイリンクス社の公式デザインサービスパートナー

・Lattice社の国内正規代理店

・自社開発による多数のFPGA評価ボード製品を保有

・年間100案件のFPGAデザインサービス実績

・放送局との協業で8K映像システム開発実績

映像システム開発に関連する課題をお抱えの場合は、弊社デザインサービスを活用いただくことで、

少しでもそれらの負荷低減を図っていただけますと幸いです。まずは下記フォームよりお気軽にお問い合わせください。

関連製品・サービス

関連記事