製品・サービス

高速アナログフロントエンドとFPGA開発

高速データコンバータとFPGAの開発から製造まで

東京エレクトロンデバイスは、プライベートブランド「inrevium(インレビアム)」のもと、FPGA開発をコア技術とした設計・量産受託サービスを提案するメーカーとしての機能を有しています。 加えてハイエンドアナログ半導体の取り扱い経験(Texas Instruments社の特約店など)を通じて、多くのアナログ・デジタルのノウハウを有しています。

高速ADCの特徴

ADC(アナログ・デジタル・コンバータ)には様々な用途があります。そのAD変換するスピードはオーディオ帯の20Hz~20kHzのアナログ信号を低サンプリング周波数で変換するものもあれば、ビデオカメラのような映像信号を高速でサンプリングするものもあります。

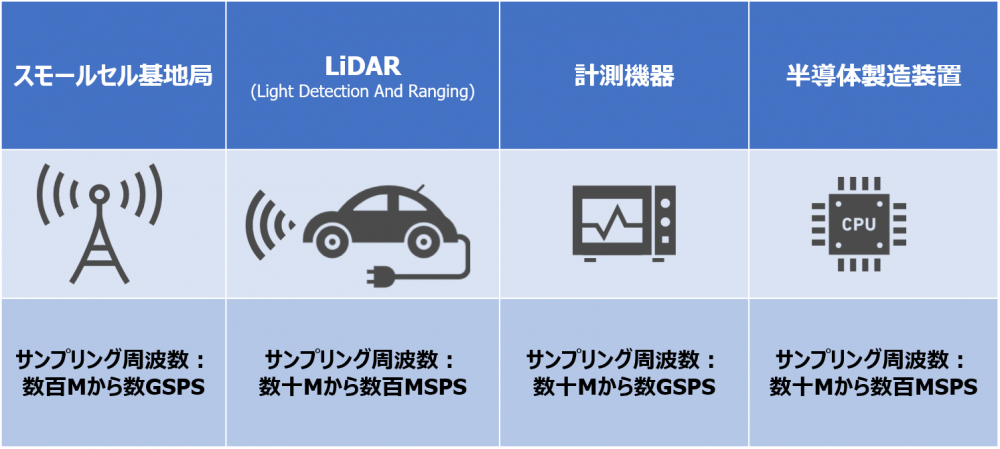

その中でも、さらに高速にアナログ信号をデジタル信号に変換しなければならないスモールセル基地局、LiDAR(Light Detection And Ranging)、計測機器、半導体製造装置等、そのサンプリング周波数は数百MSPS~数GSPSにもなります。

アプリケーション例

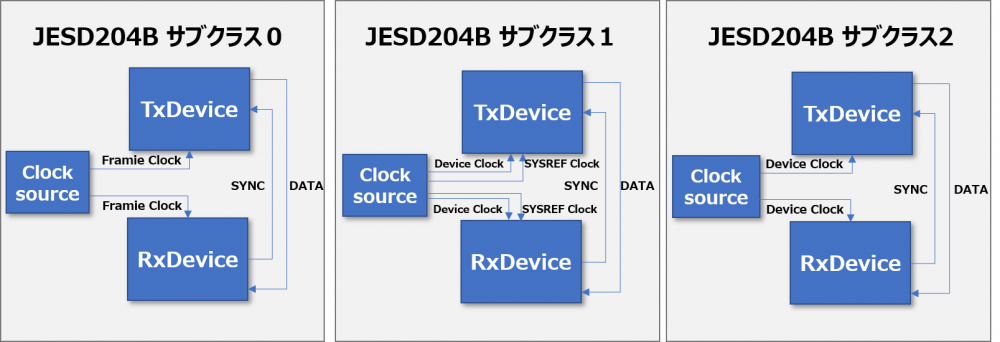

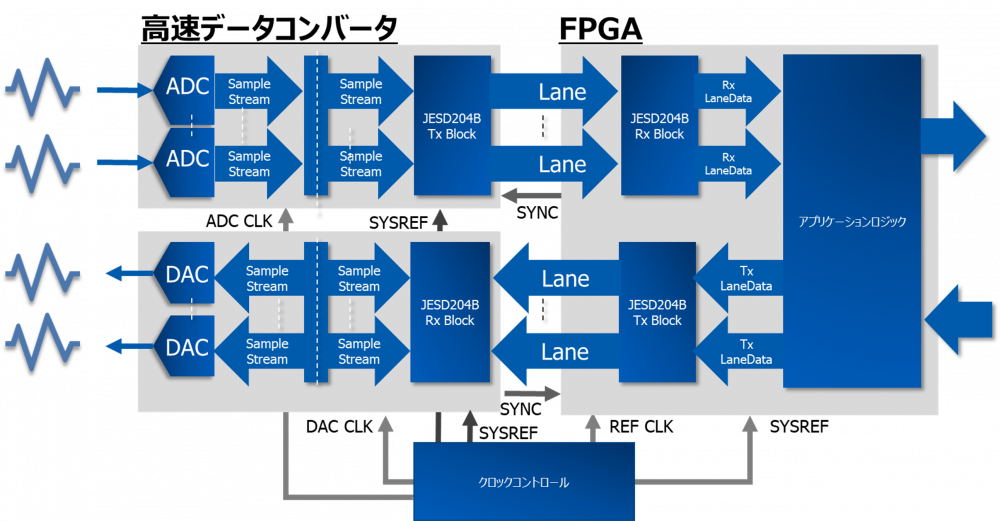

そして、そのデジタル変換後のインターフェイス規格として主流なのがJESD204B/Cです。JESD204Bではデータレートが12.5Gbpsまでサポートされており、サブクラス0ではJESD204Aとの互換性を保つためディターミニスティク・レイテンシーはサポートされておりませんが、サブクラス1と2ではサポートされています。また、JESD204Cでは最大32Gbpsまでサポートされていますが、それらのパフォーマンスを出すためには、いくつかの注意点が必要です。

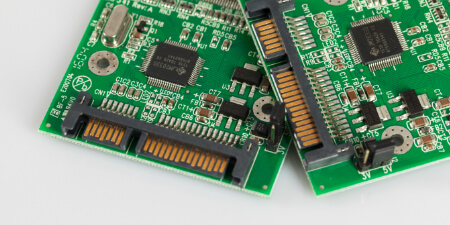

コンバータとFPGAの構成イメージ

JESD204B サブクラスごとの接続図

求められる設計ノウハウ

1. 高精度クロック

所望のパフォーマンスを確保するためには、低ジッタのクロックが必要です。各ICのデータシートの仕様を確認のうえ必要に応じてジッタクリーナを使用することで要件を満たすことができます。

2. 高効率化・低ノイズ化

以前は効率の課題がありながらもノイズの少ないLDOが使用されてきました。しかしながら近年のアナログICベンダーではノイズ特性の優れたDCDCやコンバータをリリースしており、LDOを介さずに電源を供給してもパフォーマンスに影響を与えない設計が可能になっています。DCDCであれば高効率化を実現し、消費電力の削減に寄与します。

3. レイアウト

各ICのデータシートにガイドラインの記載がありますので、可能な限り実績のあるリファレンスデザインを踏襲して使用することで設計リスクを低減します。

4. DCバランス・コーディング

JESD204xで使用されているCML(Current Mode Logic)には標準仕様がなく、通常ACカップリングして使用しますので、DCバランス・コーディングが必要となります。

5. フィルター

ADC入力部のBPFを設計する際には、ADCの入力インピーダンスも考慮してLCのパラメータを決める必要があります。事前にシミュレーションをかけ最適な定数を決定します。

開発実績

- 5GSPS対応開発ボード(2つの2.5GSPS ADCのインターリーブ構成)

- ミックスドシグナルのアプリケーション開発ボード(8ch、14bit、250MSPS)

- AD-FMCDAQ2-EBZデモ環境構築(検討用)

- レーダー向けアナログフロントエンドとドFPGA(差動信号)

- RFディテクタ

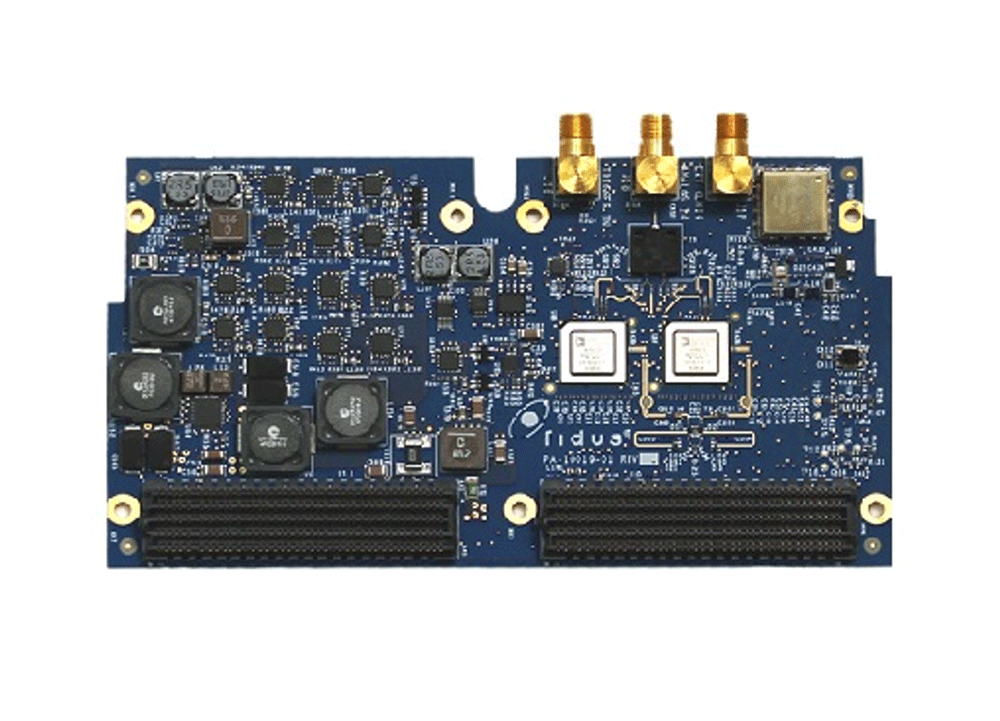

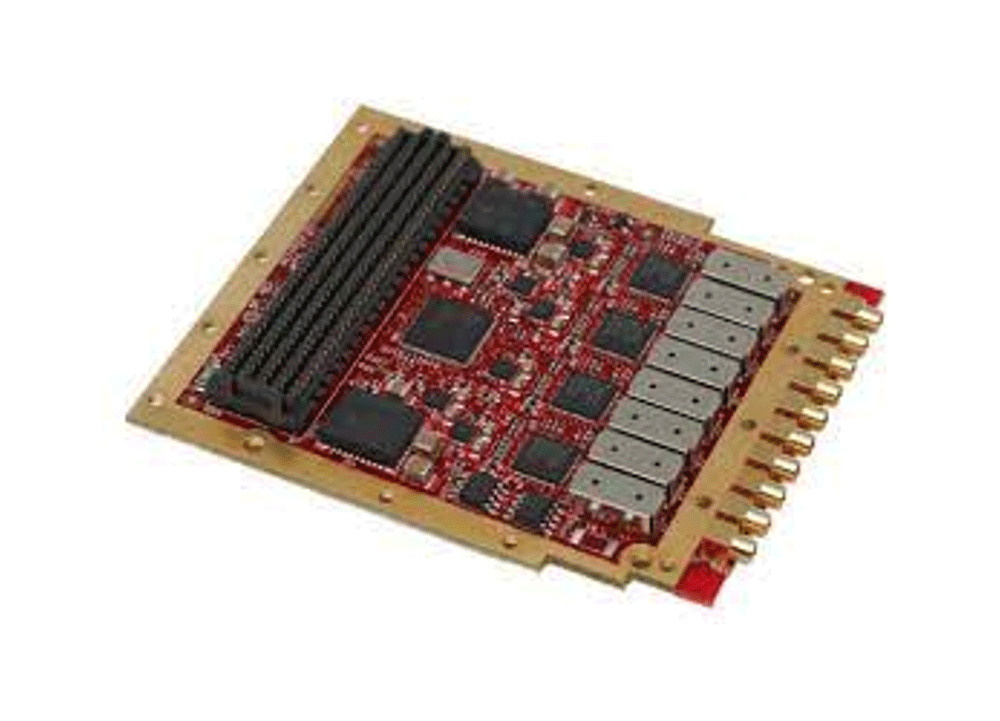

ミックスドシグナルのアプリケーション開発ボード

(型名:TB-FMCH-8AD250)

開発実績のあるデバイス

| 品番 | ICベンダ | A/Dサンプリング | A/D分解能 | A/Dch数 | 接続 インターフェイス |

アナログ フロントエンド |

|---|---|---|---|---|---|---|

| DAC5682 | テキサス・ インスツルメンツ |

1.0GSPS | 16bit | 2ch(I/Q) | LVDS | DAC |

| ADS42JBx9 | テキサス・ インスツルメンツ |

250 MSPS | 14/16 bit | 2ch | JESD204B | ADC |

| AD914x | アナログデバイセズ | 2.8 GSPS | 16bit | 4ch | JESD204B | DAC |

| AD925x | アナログデバイセズ | 80 MSPS 105 MSPS 125 MSPS |

14bit | 4ch | LVDS | ADC |

| AD926x | アナログデバイセズ | 20 MSPS 40 MSPS 65 MSPS 80 MSPS |

16bit | 1ch | Parallel, Serial SPI |

ADC |

| AD93xx | アナログデバイセズ | 250 MSPS | - | 2×2 | JESD204B | ADC/DAC |

| AD968x | アナログデバイセズ | 1.25 GSPS 1 GSPS 820 MSPS 500 MSPS |

14bit | 2ch | JESD204B | ADC |

| AD978x | アナログデバイセズ | 800 MSPS | 32bit | 2ch(I/Q) | Parallel | DAC |

| LTC2209 |

アナログデバイセズ | 160MSPS | 16bit | 1ch | Parallel CMOS, Parallel LVDS |

ADC |

| LTC2315 | アナログデバイセズ | 5 MSPS | 12bit | 1ch | SPI | ADC |

| LTC2324 | アナログデバイセズ | 2 MSPS | 12/14/16bit | 4ch | Differential, Single-Ended |

ADC |

アナログフロントエンドで変換されたデジタルデータを受け取る後段のFPGAは、接続インターフェースに応じてインテル/MAX10, Arria10、ザイリンクス/ZYNQ, Virtex-7などを使い、各ICベンダーの提供するRTL, Softwareを元に実装し必要に応じて修正して構築しています。

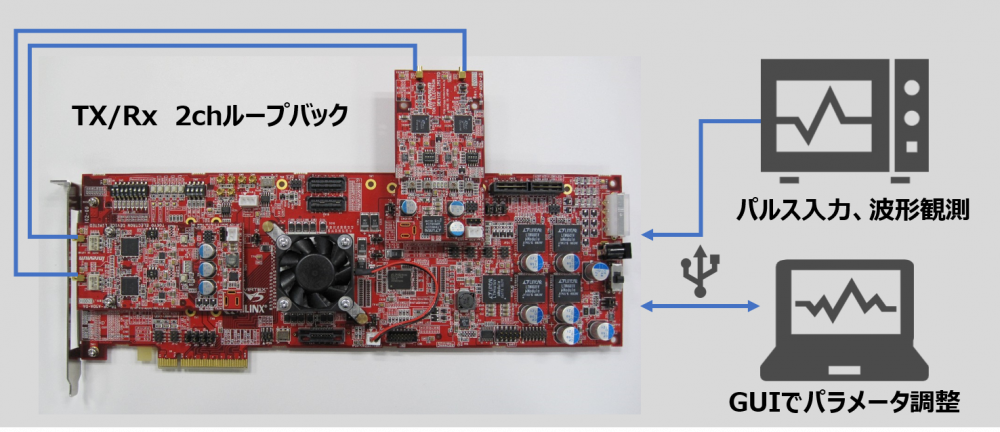

評価環境(イメージ)

接続環境:ADC/DACのループバック

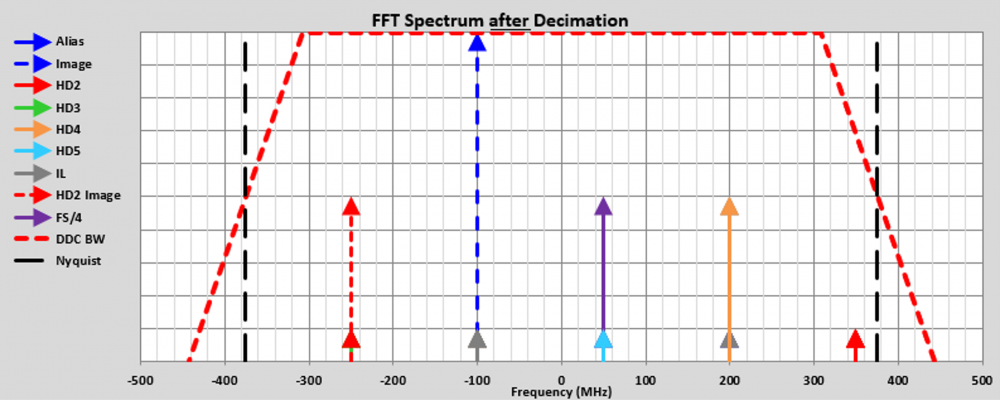

FFTスペクトラムのシミュレーション

測定機器(抜粋)

| 機器 | 型式 | ベンダー | 機能 |

|---|---|---|---|

| ネットワークアナライザー | P5020A | Keysight | 4port、9kHz~4.5GHz |

| シグナルジェネレータ | N5171B | Keysight | 9k~1GHz |

| スペクトラムアナライザ | N9010B | Keysight | 10Hz~3.6GHz |

| パワーメーター | 33511B | Keysight | 1uHz~20MHz |

| パワーメーター | N1914A | Keysight | 100kHz~6GHz |

ソリューション

高速のADCを使う上では設計開発の際に留意すべき事項が多くあります。アプリケーションによっては基板面積と実装部品の占有面積とトレードオフが発生するケースもあります。

弊社ではこれまで高速データコンバータとFPGAを組み合わせた開発を数多く行ってきており、設計ノウハウが蓄積されています。最適な部品選定、回路設計、レイアウト、定数設定、基板製造、高速通信技術などアナログ・デジタル問わず技術リソースをご提供可能です。基板製造後、機能測定やデバッグに必要な機材も多く持ち合わせています。

高速データコンバータのニーズはこれからもさらに広がっていきます。FPGAとの組み合わせで開発時間を短縮、コストのかかる設計サイクルを削減、要素検討から試作までの設計をさらに加速するご支援をいたします。

関連製品・サービス

関連記事