- HOME

- モデルベースデザインによるFPGA設計

設計 設計・製造受託

モデルベースデザインによるFPGA設計

本記事は、MathWorks Japanの川合様にご寄稿いただきました。

モデルベースデザイン (モデルベース開発, MBD) という言葉を耳にしたことはあっても、それがFPGA設計とどう関係するのか、いまひとつピンと来ない方は多いのではないでしょうか? MBDは自動車・航空宇宙産業における制御分野で既に広く用いられている設計手法ですが、実はその考え方はFPGA開発においても有効です。

FPGA開発フローにおいて、アルゴリズムの振る舞い (ビヘイビアレベル) をシミュレーションする段階と、HDLによってFPGA実装を行う段階の間に生じるギャップを感じたことはないでしょうか?この工程間の乖離により、アルゴリズムをFPGAへ実装した際に動作の整合性が取れず、検証作業に多くの時間を要します。また、仕様変更が加わると設計の大幅な見直しが必要になり、開発全体のサイクルが長期化します。

そこで力を発揮するのがMBDです。MBDでは、MATLAB®やSimulink®を用いて設計対象の動作や構造を抽象的に表現した”モデル” を作成し、シミュレーションを活用して事前に検証を行います。そして、設計の妥当性が確認されたモデルからHDLコードを自動生成してFPGA実装を進めるため、上記の工程をシームレスに接続し、このギャップを解消することが可能となります。

本記事では、まずMBDについての説明をし、つづいてMATLAB、Simulinkを活用した具体的なFPGA設計フローについて紹介します。

モデルベースデザイン (モデルベース開発、MBD) とは?

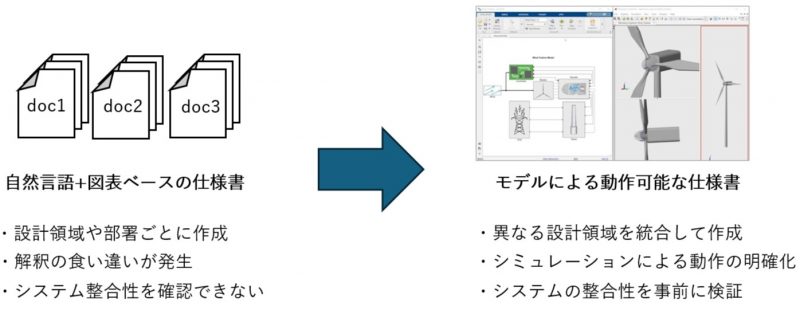

従来の開発では、自然言語+図表ベースの仕様書をもとに各領域の設計 (ソフトウェアやハードウェア) を個別に進め、最終段階での統合が一般的でした。しかしこのような手法では、解釈に食い違いが発生したり、システム設計の妥当性を早期に確認できずに開発途中での不具合や設計の不整合が発覚した場合に手戻りが大きくなるという課題がありました。

一方、MBDでは設計対象の動作や構造を 抽象的に表現した “モデル” を構築し、システム全体をシミュレーションによって事前に検証します (これは動作可能な仕様書とも呼ばれます)。つまり、設計の初期段階から仮想的な統合テストを実施し、問題点を早期に発見するというアプローチを採用します。

また、MBDでは設計の各プロセスがモデルを中心とした開発環境内で一元管理されるため、アルゴリズムの変更や要件変更に対して柔軟な対応が取りやすいという特徴があります。そして、確定したモデルからHDLコードを自動生成するため、FPGAへの実装を効率的かつシームレスに進めることができます。

このように、MBDは ”開発のフロントローディング(=シフトレフト化)” によって早期検証を実現し、アルゴリズムレベルでの品質を高めつつ、自動化による効率化も実現する設計アプローチです。昨今の複雑化するシステム開発において、MBDはエンジニアが高い抽象度で設計を構想し、迅速に実装へ結びつけるための最善のアプローチと言えます。

MATLABおよびSimulinkとは?

MBDを実現する上で中心的な役割を担うツールが、MATLAB と Simulink です。どちらもMathWorks社が提供する開発環境であり、アイデアや構想を短時間で実行可能な設計へと落とし込むことができます。

MATLAB は数値計算やデータ解析、アルゴリズム開発を得意とする科学技術計算のためのプラットフォームです。スクリプトベースで簡潔かつ柔軟に動作を記述できることが特徴です。

Simulinkは、ブロック線図ベースの視覚的な設計環境であり、システムを直感的にモデリングしながら動作をシミュレーションできるという特徴があります。コーディングを行うことなく、機能ブロックを組み合わせることで信号の流れを表現したり、制御アルゴリズムを構築でき、時間応答を含むシステムの振る舞いを容易に検証できます。さらに、MATLABで定義した関数やパラメータをそのまま利用できることも大きな強みです。

Simulinkは豊富なアドオン製品と組み合わせることで、実際のハードウェアやその設計環境とも密接に連携することが可能です。HDL Coder ™を用いれば、論理合成可能なHDLコードをモデルから自動生成してFPGAへ実装でき、 Embedded Coder ®を使えばマイコン向けに最適化された組込み用Cコードを生成することができます。これにより、モデルで検証したアルゴリズムをそのまま実機上で動作させ、シミュレーションとの動作整合性を迅速に確認することが可能です。このように、MATLABとSimulinkは単なるツールではなく、モデルをベースとして設計・検証・実装を統合的に進めるための、MBDの中核プラットフォームです。

MBDによるFPGA開発のワークフロー

HDL Coder は、合成可能なVHDL®コード、Verilog®コード、およびSystemVerilogコードをモデルから自動生成できるアドオン製品です。これを利用することで、アルゴリズム開発とFPGA実装の間に存在するギャップを最小限に抑え、モデルをベースとした一貫した設計フローを実現できます。以下に、そのフローを記載します。

アルゴリズム設計用機能モデルの作成

Simulinkなどを用いて設計対象の振る舞いを表す機能モデルを構築します。この段階では、アルゴリズムの正しさや動作を確認することが主目的であり、演算精度やハードウェア制約を意識せずに開発を進めます。つまり、浮動小数点演算を用いたシミュレーションにより、理論設計段階でアルゴリズムの特性や妥当性を検証します。

FPGA実装用モデルの作成

次に、機能モデルをFPGA実装に向けて最適化します。ここでは、ハードウェア実装に適したデータフロー構造や演算単位に修正します。また、必要に応じてHDL実装可能な機能ブロックへ置き換えたり、HDL Coderがサポートする構造に合わせてモデルを整理します。

また、FPGAを用いる場合、多くの設計では固定小数点化を行う必要があります。HDL Coderおよびアドオン製品のFixed-Point Designer™を使用すると、シミュレーション結果に基づいて最適なワード長を自動推定し、精度とハードウェアリソースのバランスを取る形でモデルの変換が可能です。変換後のモデルを再度シミュレーションして、演算誤差を確認します (※1)。

HDLコード生成

FPGA実装用モデルの検証が完了したら、HDL CoderによりVHDL/Verilog/SystemVerilogコードを自動生成します。これにより、手作業による記述ミスを防ぎながら、FPGA実装用モデルとの一貫性のある設計を維持します。

実装と検証

HDL CoderとFPGA開発ツールが連携し、合成・配置配線・ビットストリーム生成まで進めることができます。さらに、モデルと生成されたコードの等価性検証や、実機ベースの検証 (FPGA-In-the-Loop(FIL)など) を行うことが可能です。

MBDを活用したFPGA開発の実践に向けて

これまで説明したMBDによる設計フローは、アルゴリズム設計とそのFPGA実装を主軸とした開発に特に有効であり、設計品質の向上と設計期間の短縮に大きく寄与するでしょう。

一方で、HDL Coderによって生成されるコードは汎用的 (= ベンダーフリー) なHDLコードであり、デバイス固有の最適化を突き詰めた設計を行うためにはHDLやFPGA設計に関する十分な知識と経験が必要となる場合があります。

また、FPGAのインターフェイス回路やメモリ制御回路など、周辺機能についてはFPGAベンダより提供されているIPコアを用いて予め構成を定義し(※2) 、HDL Coderが生成したコードと統合することでFPGAプロジェクト全体が構築されます。

上記の詳細や導入に関しては、MathWorksまたはパートナー企業がサポートを提供しています。こうした支援を活用することで、MBDによるFPGA開発をより実践的に進めることができ、柔軟かつ高品質な設計を実現するための有効なアプローチとなります。

※1 演算精度と回路規模の最適なバランスを見つけ出すためには、このフローを繰り返し実行する必要があります。

※2 MathWorksのWebsiteにて、FPGAベンダの評価ボードをターゲットとした例が提供されているため、これらを参照した上で設計に活用することも可能です。