- HOME

- 【注目】AI時代の発展を支える半導体製造技術 「3D NAND」とは

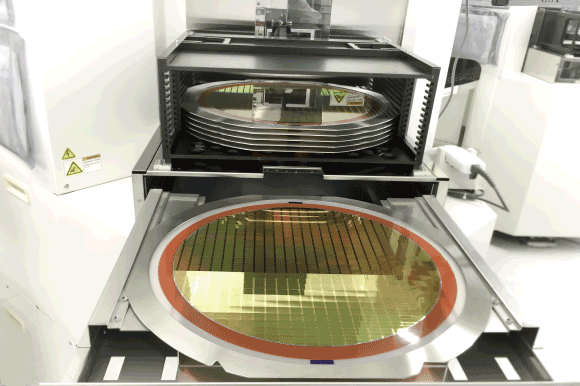

生産現場 計測・検査

【注目】AI時代の発展を支える半導体製造技術

「3D NAND」とは

先端半導体の技術の中でも微細化と並んで今後の半導体性能を大きく左右する、3次元実装技術。その構成技術である「3D NAND」 について解説します。

NANDメモリとは

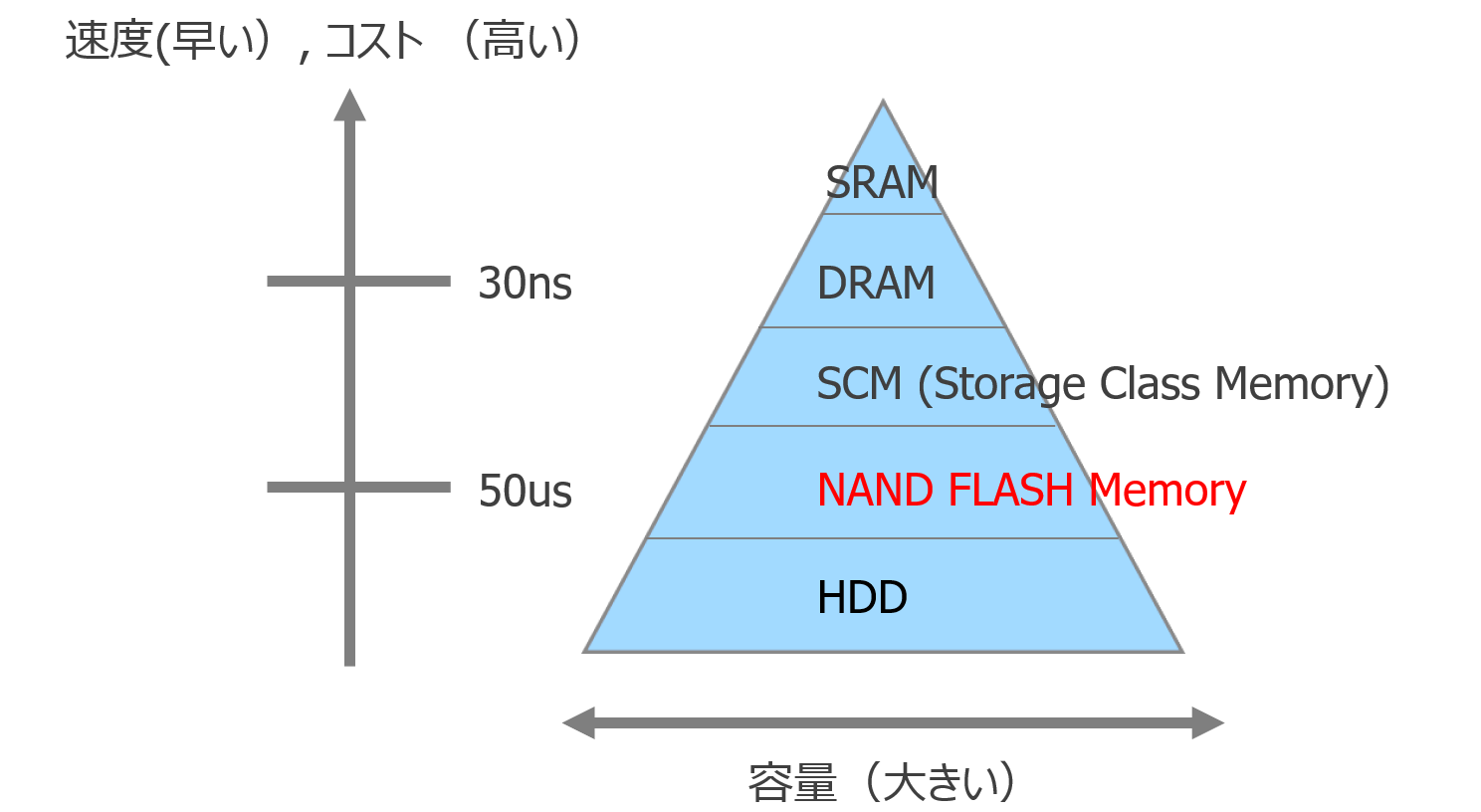

記憶媒体として、PCやスマホにも使われて我々の日常生活にもなじみ深いメモリですが、メモリには容量や読み書きの速度などによってそれぞれ特徴があり、以下のようなメモリーヒエラルキーによって現わされます。

下に行くほどメモリの容量は大きくなりますが、読み書き速度が遅くなります。一方で、上に行くほどメモリの容量は小さくなりますが、読み書き速度は速くなります。それぞれのメモリの特徴を生かして、ヒエラルキー上位のSRAM/DRAMはCPU近傍で一時記憶をにない、ヒエラルキー下位のNANDやHDDは外付けで長期記憶を担う役割を分担されています。

また、メモリ製品は電源を切るとデータが消える揮発性メモリと電源を切ってもデータが消えない不揮発性の2種類があります。NANDメモリは不揮発性メモリに分類されます。

NANDとの比較でよくでてくるメモリにDRAMがありますが、こちらは揮発性のメモリなので、電源を落とすと記録が消えてしまいます。NANDメモリは不揮発性の特性を活かし、PC、スマホ、データセンターのデータストレージとして使用されています。

NANDメモリは、1987年に東芝の舛岡富士雄氏によって開発され、同じ不揮発性メモリであるNOR型*¹の制約である高密度化を可能にするメモリとして開発されました。

他メモリと比較したときの、NANDの特徴としては大容量化や低価格化が容易な点があげられます。

メモリーセルを高密度に集積できるため、小型・軽量かつ低消費電力化が可能です。

また同じ長期記憶メモリであるHDDと比較して、機械的可動部がないため動作音がなく衝撃にも強いことから、SSDやUSBメモリ、SDカードなど幅広い機器で利用されています。書き込み/消去も高速ですが、ランダムアクセス性能*²はNOR型より劣り、書き換え寿命にも限りがあります(数千~数万回)。また、長期間のデータ保存にも限界があり、主に量とコストを重視する用途で主流となっています。

2000年代初頭までは不揮発性メモリの主力は、NOR型でしたが、NANDの持つ上記特性がスマホ向けのニーズと合致した結果一気に普及が進み、現在では長期記憶用の主流なメモリとして我々の生活において欠かせないデバイスとなっています。

メモリーヒエラルキー図

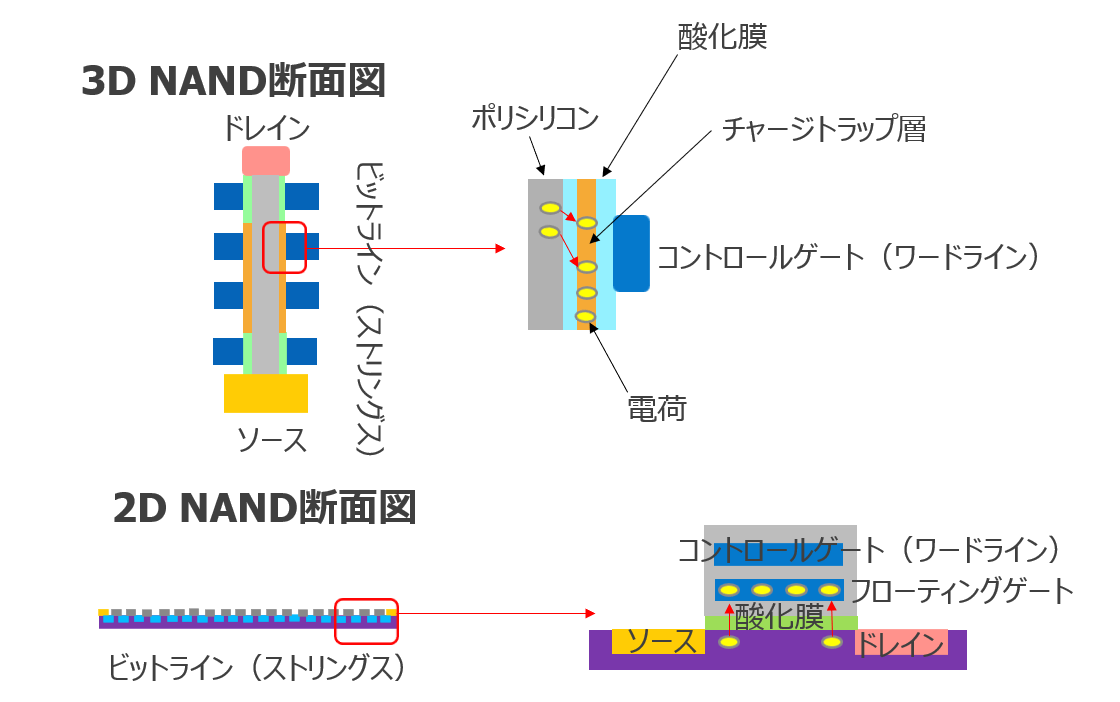

2D NANDと3D NANDの違い

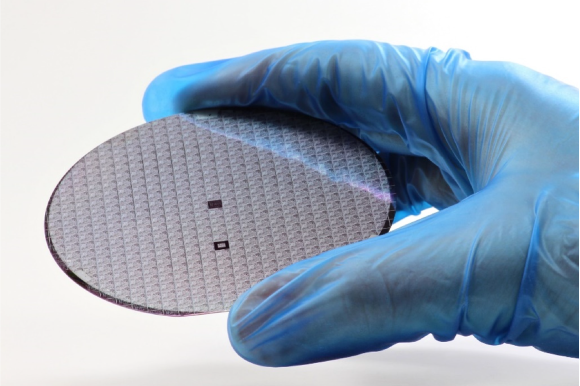

NANDメモリは元々プレーナータイプという、メモリーセルを横方向に並べて2次元的に配置した構造をしていました。

メモリーセルとは、記憶情報であるビットを記憶しておく器のようなもので、メモリーセルの数が増えるほど大量の記録ができるようになり、メモリーセルのサイズが小さくなるほど単位面積当たりのメモリの容量を増やすことができます。そのため、メモリの容量向上のためにメモリーセルの微細化のアプローチが、長年メモリ容量を増やすための主要なプロセス技術として使われてきました。

しかし、近年メモリーセルの微細化がリソグラフィー技術などの制約で物理的に困難になってきたため、微細化とは別のアプローチでセル数及び記憶容量を増やすアプローチが模索されてきました。そんな中で、開発され現在のNANDメモリの主流となっているのが3D NANDです。

3D NANDとは従来の2D NANDが横方向のみにセルを設置していたのに対し、セルを縦方向にも積層することにより、微細化に頼らずに単位面積当たりのセル数を増やすことを可能にしました。

従来の2D NANDがリソグラフィーによるセルサイズの微細化による高密度化が必要であったのに対して、3D NANDでは、セルサイズはそのままで、セルを縦方向にも積むことにより、同一面積当たりのセル数を増やしセル容量を高めることができます。

つまり、従来2D NANDでは、横方向でつながっていたビットライン(ストリング)*³が縦方向に立てられる形となって、セルを積み増すほどに容量が増える構造となっています。現在最先端向けでは300層を超えるセルの積層が行われており、メモリセルの核となるnmレベル厚の絶縁層とワード線(金属層)*⁴を数百層レベルで高精度・高均一に積み上げる成膜技術及び、積層した薄膜に対し数μm以上の深さで極細の穴(メモリホール)を垂直に開けるための超高アスペクト比(HAR)エッチング技術が大きな技術革新を占めるようになりました。

また、2D NAND方式から3D NAND方式へ移行するのにあたり従来のフローティングゲート方式からチャージトラップ方式へ、電荷の保存構造が変化しました。

チャージトラップ方式とは、SiN絶縁膜中の欠陥に電子を捕獲してデータを記憶する方式です。フローティングゲート方式と比較して製造が容易であることと、フローティングゲートより電荷移動をしにくい構造のため、多値化*⁵をしやすいという点が3D NANDにおける主なチャージトラップ方式が採用される理由です。

上記のような技術革新を経て、3D NANDでは横方向のセルサイズは2D NANDの時代20nmから同じサイズのまま2014年からの10年で約30倍の記憶密度を達成しています。

(2014年に1平方mm当たり0.93Gbitだった記憶密度は、2024年には1平方mm当たり28.5Gbitに到達)

この3D NANDによる、記憶密度向上は様々な技術革新を経ながら、今後も進んで進んでいくと考えられています。

3D NAND と2D NAND構造比較

3D NANDの今後の展望

NANDメモリの今後採用が加速することが予想されるアプリケーションとして、最有力となるのがAIサーバーやエッジAIの領域です。

AI性能を示すモデルパラメータ数はLLMの登場とともに、指数関数的に増加を続けており、パラメータを保管するためのストレージ容量も今後さらなる増加が見込まれます。また今後エッジAIが普及するにつれて、AI自体のアプリーケーションの数が増え、それを保存するためのストレージの需要も増えていきます。

NANDはHDDと比較して低消費電力かつ小型で高速応答が可能であり、DRAMと比較して記憶密度の向上による大容量化及びビット単価の低減が可能であるという特性を活かして新たなアプリケーション領域が模索されています。

上記のようにAIが社会実装されることに伴うストレージ需要増加のため、NANDも今以上の記憶密度向上が必要となります。そのための技術革新として上述した3D NANDによるセル積層手法とは別の記憶密度向上技術の採用が始まりました。

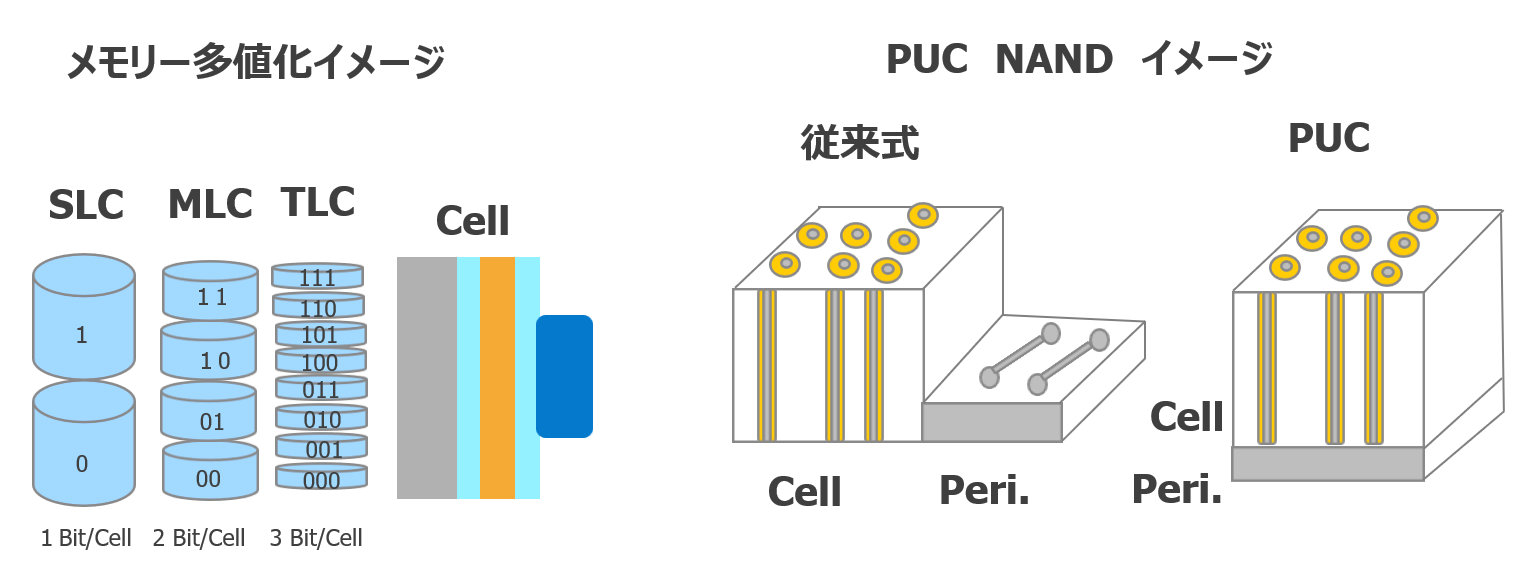

1)多値化(Penta Level Cellなど)

多値化とは、1つのメモリセルに複数ビットのデータを格納する技術で、電荷量やしきい電圧を細かく制御して情報を多段階で表現します。SLC(1ビット)からMLC、TLC、QLC(4ビット)へと進化し、同じチップ面積で記憶容量を大幅に増やせます。

従来はTLCまでが主流でしたが、急増するストレージ需要に対応するため今後は、PTCなどさらなる多値化が進むことが予想されます。

2)PUC (Periphery Under Cell array)

PUCとは、既存製造方法においてセルエリアの横に製造される周辺回路を先にダイ上に形成し、その上にセルアレイを重ねる構造です。この構造により、セルのデバイス内の占有面積を増やして記憶密度を増やすことが可能になります。しかし、PUC構造では、セルアレイの下に周辺回路を形成するため、熱処理の制限により回路性能の最適化が難しいこと、積層時の配線やアライメントが難しく歩留まり低下する点、信号経路が長くなり読み書き速度が低下しやすいという課題があります。

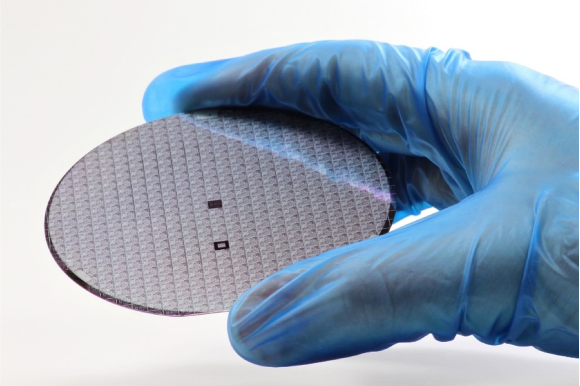

その課題を克服するため、CMOS周辺回路とメモリセルアレイを別々のシリコンウェーハで製造し、最後にウェーハ同士を高精度に貼り合わせ、一つのデバイスとするCBAと呼ばれる技術の採用も進んでいます。

NANDフラッシュメモリの採用領域は今後も高密度化と低コスト化、性能向上を両立しながら拡大が続くと見込まれています。具体的には積層数の増加やチャージトラップ方式の進化、高速なI/Fの採用で、AIデータセンターやクラウド、モバイル端末、エッジ機器まで用途が多様化し、AI処理との連携を意識した高帯域・低レイテンシなSSDや、演算処理をストレージ内で行うコンピュテーショナルストレージなども普及が予想されます。

これらの次世代材料・新構造技術の導入により、NANDはさらなる需要の拡大が見込まれます。

半導体製造現場の課題を解決!厳選ホワイトペーパー

半導体製造現場の「検査」「監視・調査」「セキュリティ」について、例を挙げて解説しています。日々の業務に是非ご活用ください。

半導体は次の次元へ 微細化から集積へ アドバンストパッケージの世界

【この資料で分かること】

- 市場と技術の未来

- アドバンストパッケージの進化

- ウェーハ加工の課題解決

【こんな方におすすめ】

半導体市場やアドバンストパッケージ技術の動向を把握したい方、製造工程やウェーハ加工における課題解決を求めている方、高速化・高密度化を実現する製造技術に興味がある方、次世代半導体の開発に関わる技術者やエンジニアの方

半導体ウェーハの外観検査まるわかりブック

【この資料で分かること】

- 多様なウェーハ材料

- ウェーハ製造工程と外観検査

- 欠陥の種類

- 検査技術のカテゴリ

【こんな方におすすめ】

Siウェーハ、化合物ウェーハ(SiC, GaN, LT/LN, InP), ガラスウェーハなどの検査に関心や課題をお持ちの方

半導体工場の現場DXガイドブック -設備の予知保全、品質監視-

【この資料で分かること】

- 半導体製造工程とDXの取組み

- 製造プロセス監視の作業自動化

- ウェーハ欠陥の原因調査

- 設備稼働監視作業の自動化

- 装置・設備・部品の故障予兆監視

【こんな方におすすめ】

ウェーハ製造工場や、デバイス製造工場のファシリティ設備の業務課題に関心や課題をお持ちの方

OTを止めるな!!半導体業界に必須のサイバー攻撃対策

【この資料で分かること】

- 外部脅威を排除しセキュアな工場へ

- 内部関係者によるリスク対策

- サプライチェーンリスク

- 横感染

- リスク発生&対策ソリューションマップ

【こんな方におすすめ】

半導体製造工場の現場、IT担当者、半導体装置メーカーでセキュリティに関心と課題をお持ちの方

用語集

*¹ NOR型:NOR型メモリは、不揮発性のフラッシュメモリで、全セルが並列接続されているため高速なランダムアクセスが可能です。データを直接実行でき、高信頼性が求められる車載機器やルーター、プリンターのファームウェア格納に利用されます。ただし書き込み速度や大容量化には不向きです。

*² ランダムアクセス性能:メモリのランダムアクセス性能とは、データの保存位置にかかわらず任意のアドレスにすばやく読み書きできる能力を指します。DRAMでは数十ナノ秒単位でアクセス可能であり、キャッシュとの組み合わせで極めて高速な応答を実現します。HDDのようなシーケンシャル型よりも、並列処理や即時アクセスに優れています。

*³ ビットライン:ビットラインは、メモリセルアレイ内で列方向に走る配線で、データの読み書きに使われる信号線です。ワードラインが選択したセルのトランジスタを介して、キャパシタの電荷状態をビットラインに伝え、センスアンプで電位変化を検出して「0」または「1」を判断します。読み出し精度や速度に大きな影響を与える重要な要素です。

*⁴ ワードライン:ワードラインは、メモリセルアレイ内で行方向に配置された配線で、各セルのトランジスタのゲートに接続されています。読み書き時に選択されたワードラインへ電圧を印加することで、その行のセルが有効化され、データがビットライン経由で読み書きされます。特定のアドレスを選択する制御信号線として動作します。

*⁵ 多値化:多値化とは、1つのメモリセルに複数ビット(2ビット=MLC、3ビット=TLC、4ビット=QLCなど)のデータを記憶させる技術です。多値化により、同じ面積内での記憶容量が増加、ビット単価が大幅に低減します。一方で、しきい値電圧の管理が複雑化し、書き込み・読み出し速度や耐久性には課題があります。