- HOME

- 【注目】 AI時代の発展を支える半導体製造技術 「ウェーハ研削加工」とは

生産現場 計測・検査

【注目】 AI時代の発展を支える半導体製造技術

「ウェーハ研削加工」とは

本シリーズで3次元実装技術について解説をしてまいりましたが、今回は番外編として、半導体デバイスの製造において非常に重要なプロセスであるウェーハ研削加工について解説します。

半導体製造現場の課題を解決!厳選ホワイトペーパー4選(無料)

ウェーハ研削加工とは

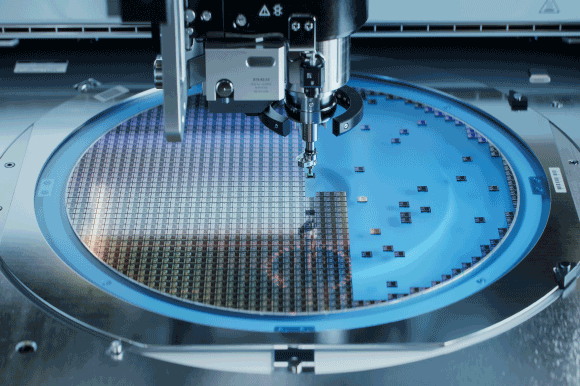

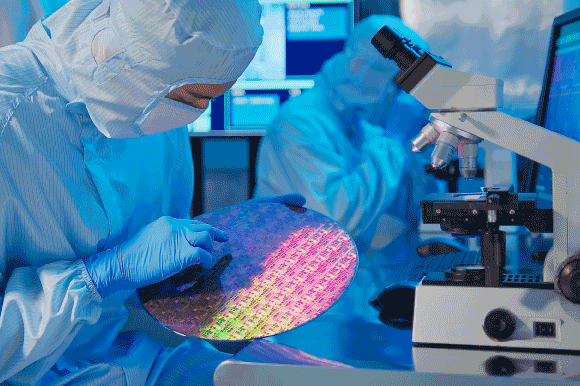

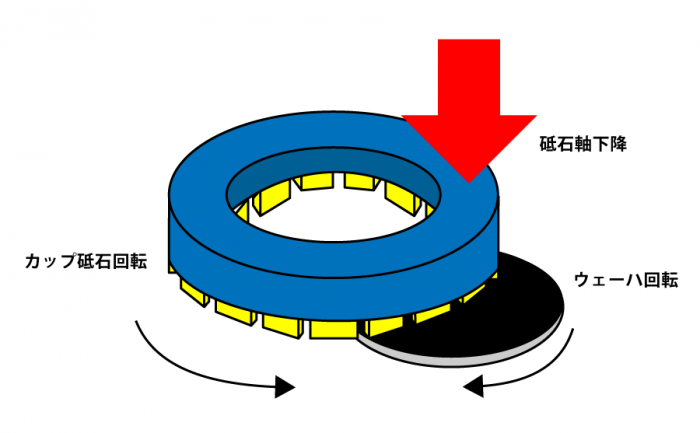

ウェーハ研削加工とは、ウェーハ薄化技術の1つであり、おもにダイヤモンド砥粒を含んだ砥石を使用してウェーハを薄く加工する技術です。半導体ウェーハ加工には、カップ砥石とよばれる円形にチップ型の砥石ボンドが配置された砥石が使用されています。

研削加工の特徴

・他のウェーハ薄化技術である研磨やエッチング加工と比べて、物理的に砥石を使用して加工するため、加工速度が速い

・in-situゲージ*¹ を用いて直接ウェーハの厚みを測定できるため、厚みの管理が容易

・砥粒によるダメージがあるため面粗さが研磨やエッチングに比べて粗い

研削加工はおもに粗加工と仕上げ加工に分かれており、粗加工では粒度の粗い砥石を使用して、目標の取り代の8割から9割を高速で加工し、残りの取り代を粒度の細かい砥石で比較的遅い速度で仕上げ加工する工程が採用されています。

研削加工によるダメージが破損等の次工程に影響を及ぼすことを考慮して、その後のダメージ除去の研磨工程とセットで加工されることも多くなっています。

ウェーハ研削のイメージ図

ウェーハ薄化手法の比較表

| 研削 | エッチング | 研磨 | |

|---|---|---|---|

| 加工速度 | 〇 | △ | × |

| ウェーハダメージ | ✕ | △ | 〇 |

| 厚み管理 | 〇 | △ | × |

ウェーハ研削加工拡大の背景

主に半導体ウェーハ薄化の目的で用いられる研削加工には、以下の2つの工程があります。

材料薄化工程

ウェーハ材料をインゴットからスライスした後、指定の規格厚みまで薄化する

バックグラインド工程

デバイスが生成された後、ウェーハをダイシングしてチップ形状に加工する前に、ウェーハのデバイス面とは反対側を薄化する

従来の使用方法に加えて、近年はデバイスの性能向上を図るために、先端パッケージの薄化工程において「研削工程」が急速に採用されています。

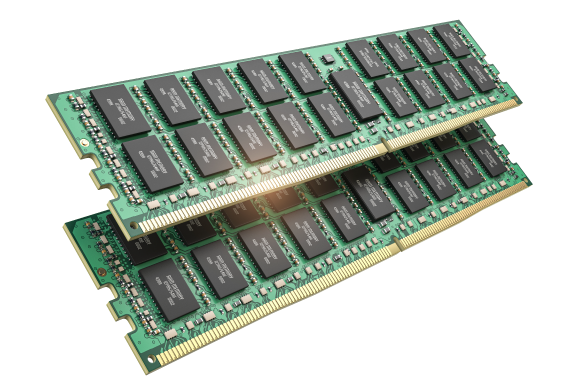

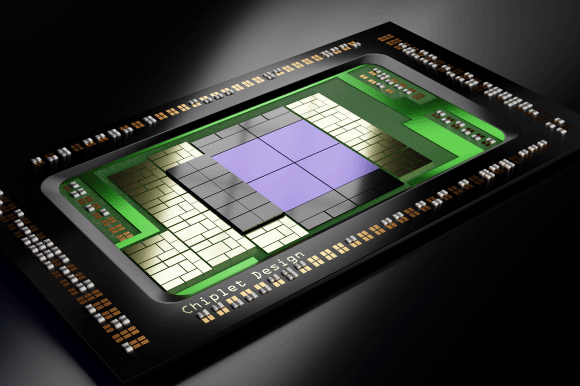

例えば、AI向け半導体を高密度集積するための基板であるシリコンインターポーザーの薄化加工に使用される他、HBM*² 向けでは研削加工で薄化したウェーハを積層することにより、広帯域のメモリー性能を達成しています。

さらに、将来的に本格的な採用が期待される、ロジックやメモリーなどの異なる性能をもつデバイスを3次元に実装する3DICにおいても、それぞれのウェーハを薄化積層することで、性能向上および省スペース、省電力化が可能になります。

3次元実装においては、TSV*³ を使用した配線が必要となり、ウェーハ厚みがそのまま配線長さとなり、性能と電力消費に直結します。そのため、いかにウェーハを薄く均等に平坦化し、積層できるかが今後のデバイス性能を大きく左右することが予想されます。

先端パッケージにおけるウェーハ研削加工の課題

先端パッケージにおけるウェーハ研削加工の課題としては以下が考えられます。

前工程に対応した、装置構成

先端パッケージでは、ウェーハ研削後に前工程に分類されるウェーハ回路工程を行うために、パーティクルや汚染を最小限に抑えた装置構成が必要となります。

薄化の限界への挑戦

現状でもウェーハの厚さを10umなどにするアプリケーションも存在しますが、今後先端半導体向けで採用が期待されるBSPDNなどはさらなるウェーハの薄化の必要性があり、ウェーハ厚み管理や、装置側の薄化対応への構造の見直しなどの進化が必要とされます。

異種材料の同時研削

ウェーハを3次元方向に積層するためには、ウェーハ内に形成されたTSVを露出させて、ウェーハ同士を接続する必要があります。そのためには、現在の加工の主流であったSi単体の加工に加えて、TSVのViaを構成するCuも同時研削する異種材研削加工が必要となります。

研削加工は半導体ウェーハ薄化加工としての歴史も長く、加工技術も確立されたものでありましたが、先端パッケージを始めとするあたらしいアプリケーションの出現により、新たな進化が必要なステージを迎えています。

ウェーハ研削加工は半導体産業の成長のために今まで以上になくてはならない存在となっており、高い経済的成長と技術革新が期待されています。

半導体製造現場の課題を解決!厳選ホワイトペーパー

半導体製造現場の「検査」「監視・調査」「セキュリティ」について、例を挙げて解説しています。日々の業務に是非ご活用ください。

半導体は次の次元へ 微細化から集積へ アドバンストパッケージの世界

【この資料で分かること】

- 市場と技術の未来

- アドバンストパッケージの進化

- ウェーハ加工の課題解決

【こんな方におすすめ】

半導体市場やアドバンストパッケージ技術の動向を把握したい方、製造工程やウェーハ加工における課題解決を求めている方、高速化・高密度化を実現する製造技術に興味がある方、次世代半導体の開発に関わる技術者やエンジニアの方

半導体ウェーハの外観検査まるわかりブック

【この資料で分かること】

- 多様なウェーハ材料

- ウェーハ製造工程と外観検査

- 欠陥の種類

- 検査技術のカテゴリ

【こんな方におすすめ】

Siウェーハ、化合物ウェーハ(SiC, GaN, LT/LN, InP), ガラスウェーハ等の検査に関心や課題をお持ちの方

半導体工場の現場DXガイドブック -設備の予知保全、品質監視-

【この資料で分かること】

- 半導体製造工程とDXの取組み

- 製造プロセス監視の作業自動化

- ウェーハ欠陥の原因調査

- 設備稼働監視作業の自動化

- 装置・設備・部品の故障予兆監視

【こんな方におすすめ】

ウェーハ製造工場や、デバイス製造工場のファシリティ設備の業務課題に関心や課題をお持ちの方

OTを止めるな!!半導体業界に必須のサイバー攻撃対策

【この資料で分かること】

- 外部脅威を排除しセキュアな工場へ

- 内部関係者によるリスク対策

- サプライチェーンリスク

- 横感染

- リスク発生&対策ソリューションマップ

【こんな方におすすめ】

半導体製造工場の現場、IT担当者、半導体装置メーカーでセキュリティに関心と課題をお持ちの方

用語集

- *¹ in-situゲージ

- in-situゲージとは製造プロセス中に、製品の寸法や品質をリアルタイムで監視測定するゲージです。

- *² HBM

- HBM(High Bandwidth Memory)は高速で大容量のデータ転送を可能にする次世代メモリ技術です。

- *³ TSV

- TSV(Through-Silicon-Via)はシリコンウェーハを貫通する垂直配線のことです。