- HOME

- 【注目】 AI時代の発展を支える半導体製造技術 「UCIe」とは

生産現場 計測・検査

【注目】 AI時代の発展を支える半導体製造技術

「UCIe」とは

UCIeとは

UCIe(Universal Chiplet Interconnect Express)とは、チップレット間の高速相互接続を実現するための新しい業界標準規格の名称および同規格を策定推進する団体名を指します。

UCIeの参加企業の特色としては、業種業界の垣根を超えた幅広い企業が参画していることが挙げられます。また、通常は競合関係にある企業が協力して標準化を進めている点が特徴的です。

具体的にはIntel、AMD、Arm、Qualcomm、Samsung、TSMCなどの主要な半導体企業のみならず、 Google Cloud、Microsoft、Meta (Facebook)、Alibabaなどのクラウドサービスプロバイダー*¹、ArmなどのIPサプライヤー、EDAサプライヤー、ASEなどのパッケージ専門企業も参加しております。

さらに、今後の自動運転含む半導体技術のさらなる採用が期待される自動車業界の企業も名を連ねています。

これらの特色から、UCIeが幅広い業界のサポートを得て、チップレット技術の標準化と普及を推進していることがわかります。多様な企業の参加により、相互運用性の高い柔軟なチップレットエコシステムの構築が期待されています。

上記参加企業の標準化活動の成果として、2022年3月に標準規格としてUCIe1.0が発表されました。この規格により、将来的に異なるベンダーが製造したチップレット(小型チップ=ダイ)を1つのパッケージに統合することが可能であることを示唆しています。

この標準規格を通じて、複数のチップを組み合わせて、高性能かつ効率的なシステムオンチップ(SoC)を構築できるようになることが期待されています。

Chipletの概略図

![]()

UCIe発足の背景

UCIeの発足の背景としては、AI需要を主因とするコンピューティング能力向上要求に対応するために、従来の1つのチップにさまざまな機能を搭載するSoC*² から、チップを機能毎に分割し、パッケージ基板上などで再接続するチップレット技術の採用が進んできていることがあります。

チップレット技術においては、分割したダイ(チップ)は分割したままでは動作せず、パッケージ基板上で再度、2次元、3次元的に相互接続することでSoCの機能を再現します。

そのため、従来の技術では必要がなかったパッケージ基板上の異なるダイを高速、低消費電力で接続する必要と、別メーカーで製造されたダイ同士がパッケージ基板上で相互接続できるように規格の標準化が求められてきたのです。

具体的には、以下の標準化された規格により、異なるベンダーや製造プロセスのダイを効率的に相互接続し、高性能で柔軟なシステム構築を可能にしています。

- 物理I/O層の標準化 電気信号、クロック、データレートの管理

- プロトコル層の標準化 PCIe*³、CXL*⁴ およびカスタムプロトコルのサポート

- フォームファクター*⁵ の標準化 ダイのサイズ、バンプの位置、バンプのピッチなど

- マネジメントの標準化 ソフトウェアの標準化、テスト方法の標準化など

標準化の分類図

![]()

UCIeの今後の展望

UCIeの今後の展望についてですが、現在は主に、パッケージ基板上での2D/2.5Dでのダイ相互接続をメインターゲットとして規格が制定されていますが、さらなる性能向上のためダイを垂直に重ね合わせる3D接続においても、今後は標準化の動きがあります。

また、現在のサーバー向けAI用途とは別でPC、スマホ、自動車など、それぞれのデバイスにAIが搭載されるエッジAIの採用も今後加速するとみられ、それぞれに適したチップレット構造とその標準化が必要になると考えられます。

これらの新しい時代のデバイスの開発を加速させるうえで、UCIeによるチップレット接続の標準化は欠かせません。

以上のようにチップレット技術は、自動車産業からデータセンター、高性能コンピューティング、モバイルデバイスに至るまで、幅広い分野での技術革新と、市場のニーズに対応する柔軟なソリューションを提供することが期待されています。

その中でUCIeは、半導体業界全体における設計と製造の手法を変革し、新しいエコシステムの形成と持続可能な技術の発展を促進する重要な要素となることが期待されています。

半導体製造現場の課題を解決!厳選ホワイトペーパー

半導体製造現場の「検査」「監視・調査」「セキュリティ」について、例を挙げて解説しています。日々の業務に是非ご活用ください。

半導体は次の次元へ 微細化から集積へ アドバンストパッケージの世界

【この資料で分かること】

- 市場と技術の未来

- アドバンストパッケージの進化

- ウェーハ加工の課題解決

【こんな方におすすめ】

半導体市場やアドバンストパッケージ技術の動向を把握したい方、製造工程やウェーハ加工における課題解決を求めている方、高速化・高密度化を実現する製造技術に興味がある方、次世代半導体の開発に関わる技術者やエンジニアの方

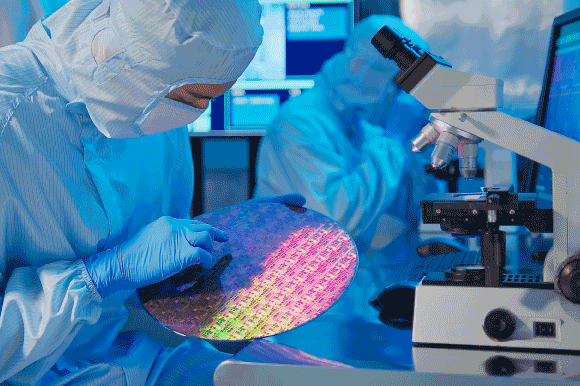

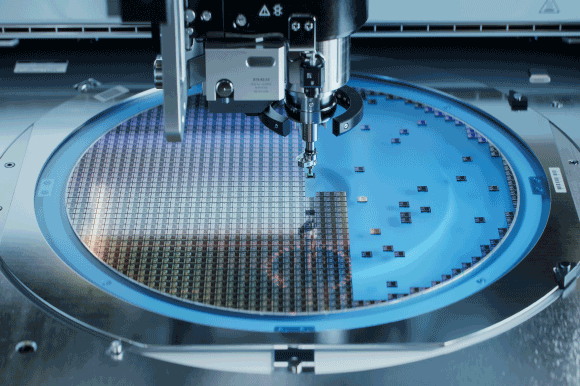

半導体ウェーハの外観検査まるわかりブック

【この資料で分かること】

- 多様なウェーハ材料

- ウェーハ製造工程と外観検査

- 欠陥の種類

- 検査技術のカテゴリ

【こんな方におすすめ】

Siウェーハ、化合物ウェーハ(SiC, GaN, LT/LN, InP), ガラスウェーハ等の検査に関心や課題をお持ちの方

半導体工場の現場DXガイドブック -設備の予知保全、品質監視-

【この資料で分かること】

- 半導体製造工程とDXの取組み

- 製造プロセス監視の作業自動化

- ウェーハ欠陥の原因調査

- 設備稼働監視作業の自動化

- 装置・設備・部品の故障予兆監視

【こんな方におすすめ】

ウェーハ製造工場や、デバイス製造工場のファシリティ設備の業務課題に関心や課題をお持ちの方

OTを止めるな!!半導体業界に必須のサイバー攻撃対策

【この資料で分かること】

- 外部脅威を排除しセキュアな工場へ

- 内部関係者によるリスク対策

- サプライチェーンリスク

- 横感染

- リスク発生&対策ソリューションマップ

【こんな方におすすめ】

半導体製造工場の現場、IT担当者、半導体装置メーカーでセキュリティに関心と課題をお持ちの方

用語集

- *¹ クラウドサービスプロバイダー

- クラウドサービスプロバイダーは、インターネット経由でデータ保存、コンピューティングリソース、アプリケーションサービスなどを提供する企業です。代表的な企業として、AMAZON、GOOGLE、METAなどの企業が挙げられます。

- *² SoC

- SoC(システム・オン・チップ)とは、CPU、メモリ、周辺機器などの主要なコンポーネントを単一のチップに統合した集積回路です。これにより、コンパクトで省電力な電子機器が実現します。

- *³ PCIe

- PCIe(Peripheral Component Interconnect Express)とは、コンピュータのマザーボードと周辺機器(グラフィックカード、SSDなど)を高速に接続するためのインターフェース規格です。

- *⁴ CXL

- CXL(Compute Express Link)とは、CPUとその他のコンピュータ部品(メモリ、アクセラレータ、ストレージなど)の間で低レイテンシーかつ高帯域幅でデータを転送するためのインターフェース規格です。

- *⁵ フォームファクター

- フォームファクターとは、電子機器や部品の物理的なサイズや形状、設計基準を指す用語です。例えば、コンピュータのマザーボードやハードドライブなどの標準的な寸法や取り付け方法を規定し、互換性と交換性を確保します。