- HOME

- 【注目】AI時代の発展を支える半導体製造技術 「2.5次元実装技」とは

生産現場 計測・検査

【注目】AI時代の発展を支える半導体製造技術

「2.5次元実装技」とは

先端半導体の技術の中でも微細化と並んで今後の半導体性能を大きく左右する、3次元実装技術。その構成技術のである2.5次元実装技術について解説します。

2.5次元実装技術拡大の背景は?

トランジスターの誕生以降現在にいたるまで半導体の成長をけん引してきた基本原理は、1枚の半導体チップに集積するトランジスタ数を増やすムーアの法則でした。

ムーアの法則により2年間で1枚のチップに搭載されるトランジスタが2倍に増加することにより、システムの製造コストは大幅に低下し、また動作周波数等の半導体の性能は性能はアップしてきました。

また技術的には1枚のチップに多くの機能を搭載するSoC(System on a Chip)*¹と呼ばれるモノリシックIC*²化技術が進展してきました。

しかしながらムーアの法則がスローダウンするにしたがい、1枚あたりのチップコストは増加を続け、より多くのトランジスタをワンチップに詰め込むことの意義は、薄れてきました。

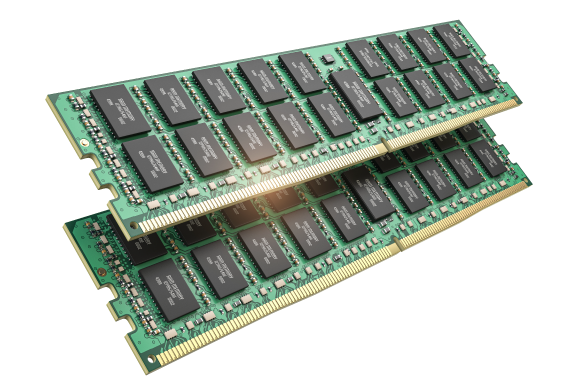

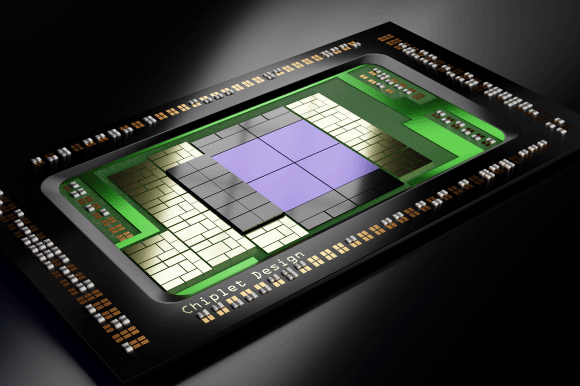

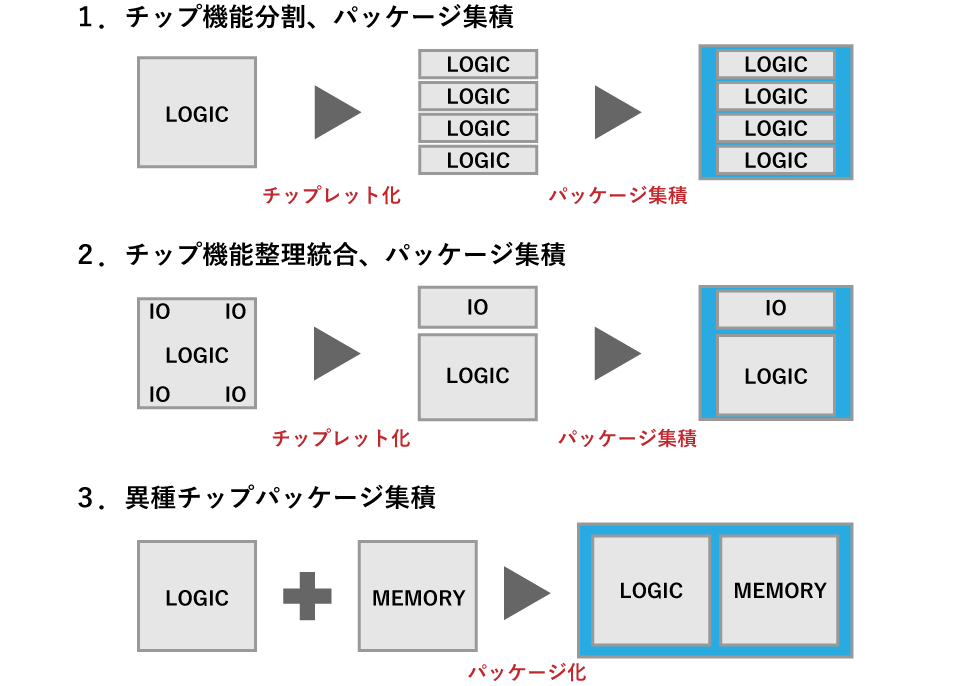

そこでムーアの法則を拡張するため、チップレット*³と呼ばれるモノリシック化していない複数の半導体チップを1つのパッケージにまとめることで、システム化する新しい世代のパッケージング技術がスマホ、HPCをはじめとする先端半導体用途で採用されてきています。

複数の半導体チップを1個のパッケージに集積化する3つの事例

2.5次元実装技術に必要な技術とは

最先端のパッケージング技術に求められるのは、外形寸法をワンチップと近い水準にまで小さくするとともに、消費電力を低減し、性能を高め、多くの機能を収容することです。

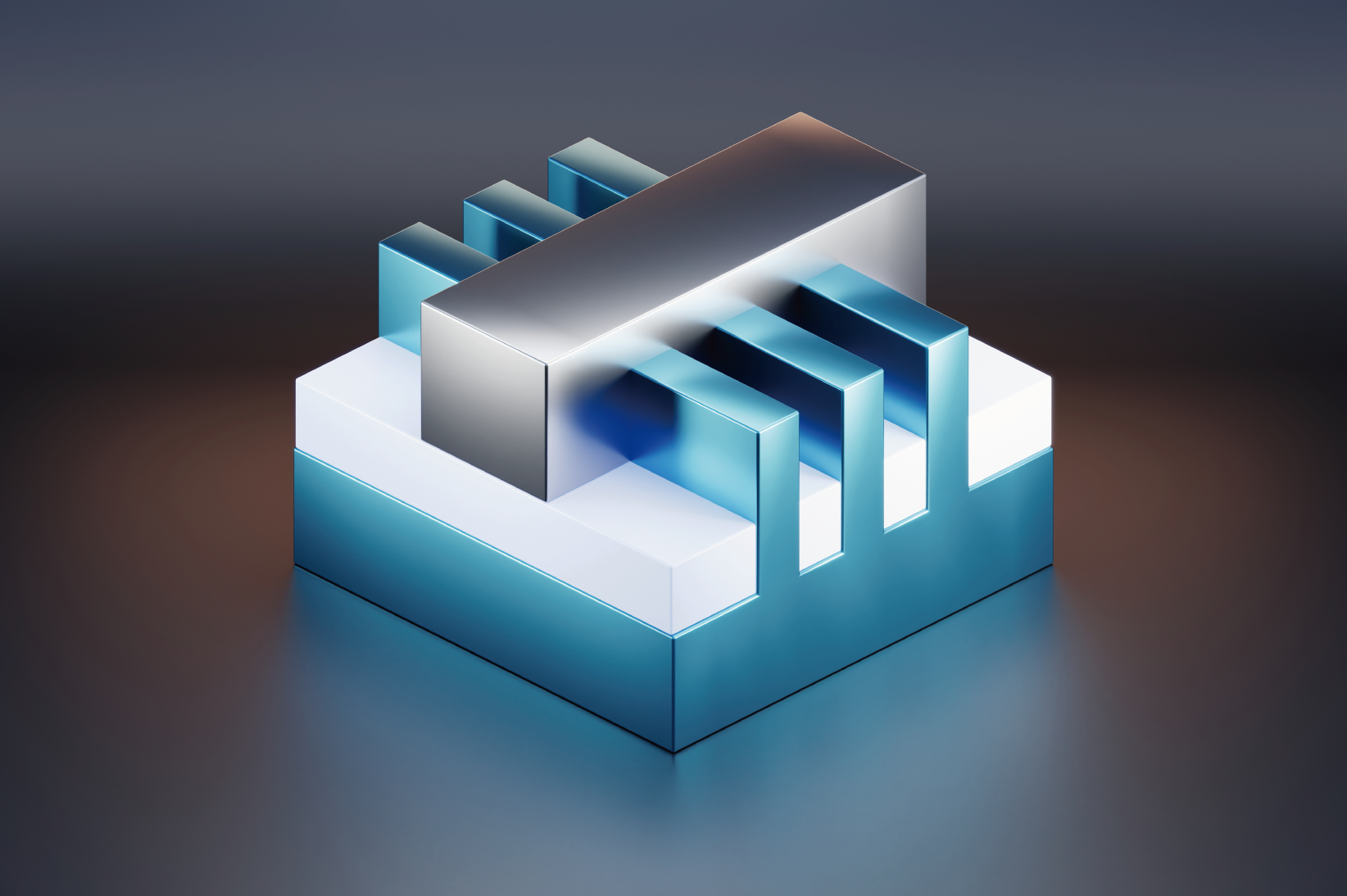

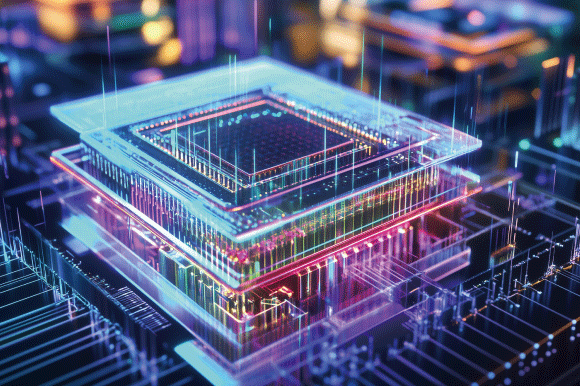

そこで登場したのが2.5次元実装とよばれるインターポーザー基板を介して、その上に複数のシリコンダイを横に近接して並べるチップ実装する技術です。

高性能半導体向けには主にSiがインターポーザーとして使用されています。

シリコンインターポーザの表面(上側)には、RDL*⁴と呼ばれる多層配線の回路を形成してありRDL層でチップ同士を接続します。また、TSV*⁵によって裏面(下側)の樹脂基板と接続します。

シリコンインターポーザーが高性能半導体向けに使用される理由ですが、SoCと同等の性能をパッケージ上で再現するには、チップ間の距離をなるべく詰めて配置する必要があり、樹脂基板では困難なRDL微細配線をシリコン上で形成するためです。

またシリコン基板の上にシリコンダイを載せるので、熱膨張係数の違いによるウェーハ反りが発生しずらく、複数のチップをインターポーザー上に実装すること可能です。

半導体チップ2.5次元集積のイメージ図(側面側)

![]()

2.5次元実装技術の課題とは

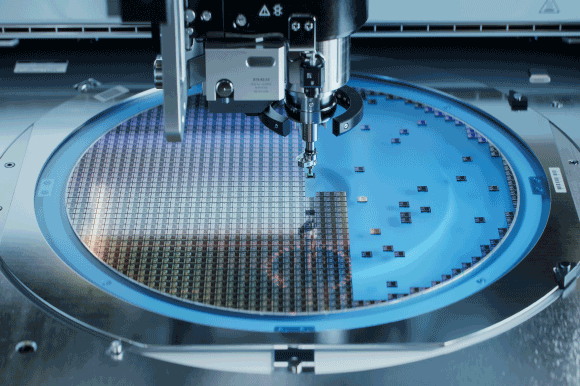

Siインターポーザーを使用した2.5次元実装の課題としてはコストおよび、実装面積の拡大があります。

最新のSiインターポーザの大きさは単純計算では約3400mm2(約58.6mm角)に達すると言われておりSi自体の材料費および、微細なバンプでシリコンダイとシリコンインターポーザを接続したり配線等のプロセスコストも増加しています。

コストを削減するため、インタポーザーにSiではなく樹脂を使用するなど新しい技術も発展し、3次元実装と合わせて実装面積を少なくする技術の需要も増えてきています。現在のHPC、スマホ用途だけなく、今後はエッジコンピューティング用途でも需要が拡大するため用途に合わせた実装面積と安価な製造プロセスの開発が必要となってくると考えられています。

半導体製造現場の課題を解決!厳選ホワイトペーパー

半導体製造現場の「検査」「監視・調査」「セキュリティ」について、例を挙げて解説しています。日々の業務に是非ご活用ください。

半導体は次の次元へ 微細化から集積へ アドバンストパッケージの世界

【この資料で分かること】

- 市場と技術の未来

- アドバンストパッケージの進化

- ウェーハ加工の課題解決

【こんな方におすすめ】

半導体市場やアドバンストパッケージ技術の動向を把握したい方、製造工程やウェーハ加工における課題解決を求めている方、高速化・高密度化を実現する製造技術に興味がある方、次世代半導体の開発に関わる技術者やエンジニアの方

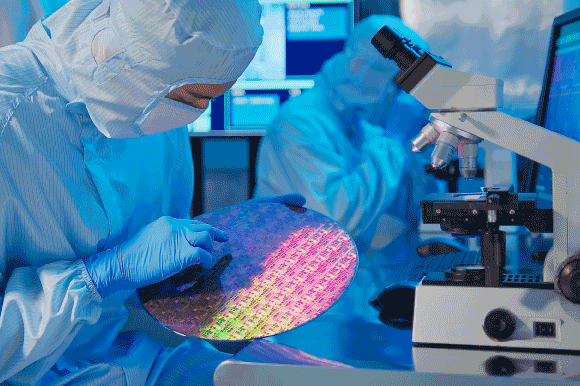

半導体ウェーハの外観検査まるわかりブック

【この資料で分かること】

- 多様なウェーハ材料

- ウェーハ製造工程と外観検査

- 欠陥の種類

- 検査技術のカテゴリ

【こんな方におすすめ】

Siウェーハ、化合物ウェーハ(SiC, GaN, LT/LN, InP), ガラスウェーハ等の検査に関心や課題をお持ちの方

半導体工場の現場DXガイドブック -設備の予知保全、品質監視-

【この資料で分かること】

- 半導体製造工程とDXの取組み

- 製造プロセス監視の作業自動化

- ウェーハ欠陥の原因調査

- 設備稼働監視作業の自動化

- 装置・設備・部品の故障予兆監視

【こんな方におすすめ】

ウェーハ製造工場や、デバイス製造工場のファシリティ設備の業務課題に関心や課題をお持ちの方

OTを止めるな!!半導体業界に必須のサイバー攻撃対策

【この資料で分かること】

- 外部脅威を排除しセキュアな工場へ

- 内部関係者によるリスク対策

- サプライチェーンリスク

- 横感染

- リスク発生&対策ソリューションマップ

【こんな方におすすめ】

半導体製造工場の現場、IT担当者、半導体装置メーカーでセキュリティに関心と課題をお持ちの方

用語集

- *¹ SoC(System on a Chip)

- SoC とは共通の目的にあわせてさまざまなコンピュータに必要とされる電子回路を単一の統合チップ(IC)に組み込んだLSIのことです。一例としては、中央演算処理装置(CPU)、メモリ・インターフェース、オンチップ入出力装置、入出力インターフェース、二次記憶装置インターフェースにて構成されます。

- *² モノリシックIC

- SoCに代表される、複数機能をもつ半導体ICを1つのチップ上にまとめた電子回路のことでです。

- *³ チップレット

- チップレットは、SoCとして、1チップ上に構成されている各ICを機能に応じて、複数チップに分割したものです。インターポーザー上で他のチップレットと組み合わせて、1つのパッケージに収められるように設計されています。チップレットのセットは、「レゴのような」組み立てで実装することができます。

- *⁴ RDL

- Redistribution layerの略称で、再配線層の意味です。Cuと絶縁層で構成されており、各チップと外部基板を電気的に接続する層です。

- *⁵ TSV

- Through-silicon viaの略称で Si貫通電極の意味です。シリコンウェーハまたはダイを完全に貫通する垂直な電気接続ビアです。TSVは、ワイヤーボンドやフリップチップに代わる高性能な配線技術として、3次元パッケージや3次元集積回路の作成に使用されています。従来のワイヤーボンド接続に比較して、配線やデバイスの密度が大幅に向上し、接続の長さも短くなります。