- HOME

- 【注目】AI時代の発展を支える半導体製造技術「BPR(Buried Power Rail)」とは

生産現場 計測・検査

【注目】AI時代の発展を支える半導体製造技術

「BPR(Buried Power Rail)」とは

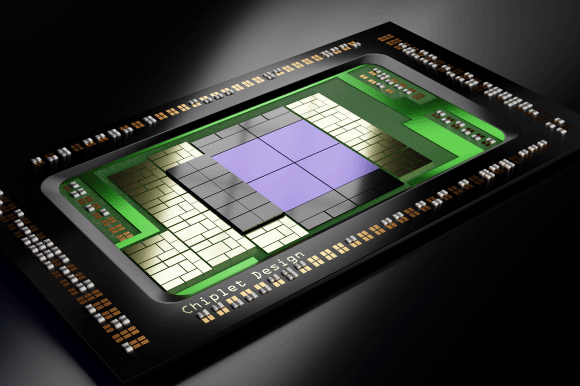

先端半導体の技術の中でも微細化と並んで今後の半導体性能を大きく左右する、3次元実装技術。 その構成技術のである BPR(Buried Power Rail)について解説します。

半導体製造現場の課題を解決!厳選ホワイトペーパー4選(無料)

BPR(Buried Power Rail)とは

BPR(Buried Power Rail)とは、PCBやパッケージ基板等の外部から供給された電源をデバイス全体に配給するPower Railをデバイスの上部の配置から、デバイス下部のサブストレートや絶縁層内に埋め込み再配置する技術です。現在主に、5nm以下の最先端ノードのデバイスで採用が始まっています。

本技術を採用することにより、デバイスの微細化をさらに進めるとともに、安定した電源供給が可能となり、先端デバイスの能力を最大源に引き出すことが可能になります。

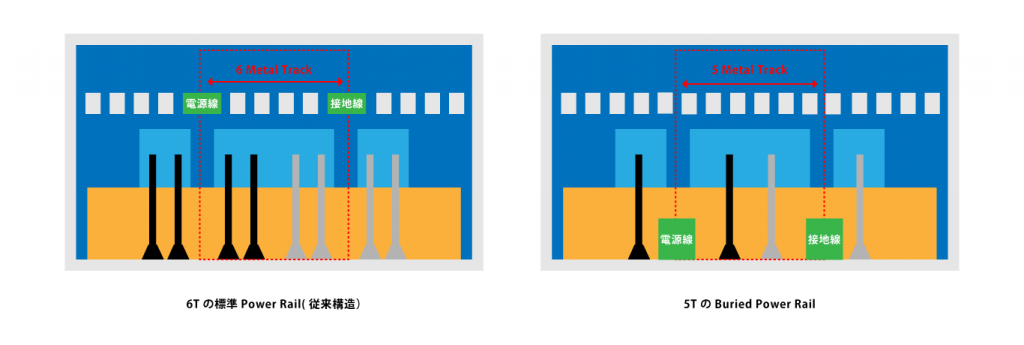

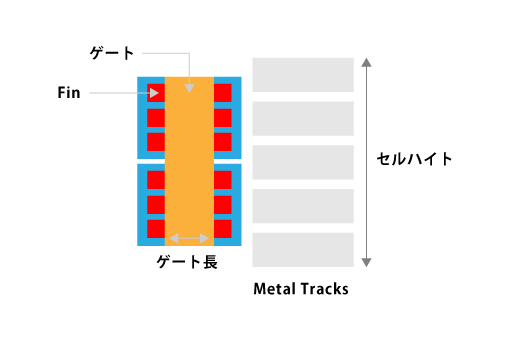

具体的には、従来デバイス上部に設置されていた配線層(電源線、接地線、信号線)から電源線、接地線をデバイス下部に埋め込むことで、信号線のみをデバイス上部に残し、配線数を少なくすることができます。(メタルトラック*¹ の削減)

それにより、デバイスの全体のサイズを小さくすることが可能になります。(セルハイト*² の低減)

また、BPRの電源/接地配線はアスペクト比(縦/横比)を高くできるので、電気抵抗を低くすることができ、IRドロップ*³ の低減に貢献します。

BPR採用の背景

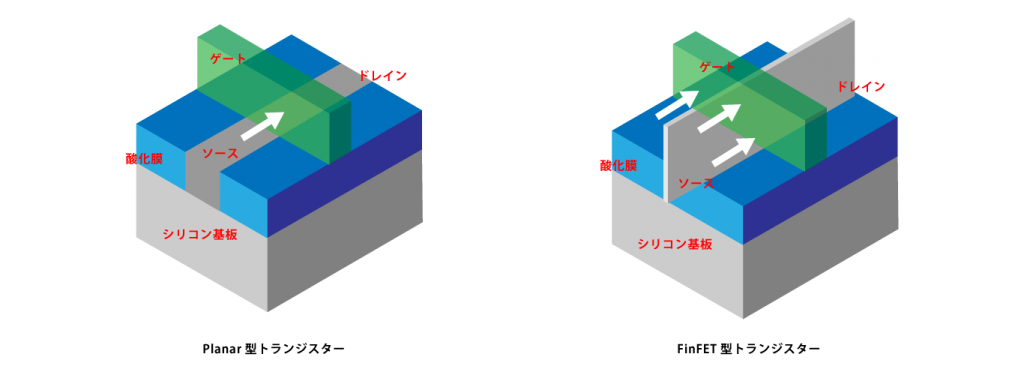

BPR採用の背景としては、従来の平面的な構造のMOSトランジスタは28nm世代~22nm世代の技術ノードで短チャンネル効果*⁴ のため、微細化が困難になり、16/14nm世代以降の技術ノードではFinFET(フィンフェット)と呼ばれる立体的な構造のMOSトランジスタが採用されてきたことがあります。

FinFETは、3Dのフィン構造を持つことで、ゲートがチャンネルを3方向から包み込みます。

この結果、短いゲート長でもチャンネルをしっかりと制御できるようになり、短チャンネル効果を大幅に緩和することができるようになりました。

しかしながら、Finfet構造でも、短チャンネル効果のため、ゲート長をいままでのように縮小できないため、その代わりに、スタンダードセル*⁵ の高さ(セルハイト)を短くすることでの微細化への対応が検討されました。

セルハイトは、フィンと同じ方向(水平方向)に走る最下層金属配線(M0あるいはM1)の本数(メタルトラック数)で決まるため、この最下層の金属配線に含まれる電源線と接地線をデバイス下部に埋め込むことによってセルハイトを低減し、微細化対応を行う流れとなっています。

上記のような背景で、先端ノード向けでBPRの採用が始まっています。

従来構造(Planar)とFinFETの比較イメージ

従来構造とBPRの比較イメージ(断面図)

FinFETセル構造上面図

BPRの課題と展望

BPRは、先進的な半導体デバイスでの配線密度を高め、静電的ノイズやパワーノイズを低減するための技術として注目されています。しかし、この技術には取り組むべき課題が存在します。

課題

- 製造の複雑さ:BPRの実装は製造工程の追加や変更を必要とし、製造の複雑さを増大させる可能性があります。

- 熱的問題:埋め込まれた電源ラインは熱の拡散を阻害する可能性があり、デバイスの熱的挙動に影響を及ぼすリスクがあります。

- インテグレーション:現存する製造プロセスやデザインフローとの統合課題となることが考えられます。

上記課題はありますが、BPRは、半導体デバイスの性能向上と製造効率の向上の双方を目指す今後の技術的な取り組みの一部として、重要な位置を占めると考えられています。

今後は、熱伝導性や電気伝導性に優れた新しい材料や、BSPDN*⁶ やナノTSV*⁷ などの新しいプロセス技術との融合で半導体のさらなる進化に貢献することが期待されています。

半導体製造現場の課題を解決!厳選ホワイトペーパー

半導体製造現場の「検査」「監視・調査」「セキュリティ」について、例を挙げて解説しています。日々の業務に是非ご活用ください。

半導体は次の次元へ 微細化から集積へ アドバンストパッケージの世界

【この資料で分かること】

- 市場と技術の未来

- アドバンストパッケージの進化

- ウェーハ加工の課題解決

【こんな方におすすめ】

半導体市場やアドバンストパッケージ技術の動向を把握したい方、製造工程やウェーハ加工における課題解決を求めている方、高速化・高密度化を実現する製造技術に興味がある方、次世代半導体の開発に関わる技術者やエンジニアの方

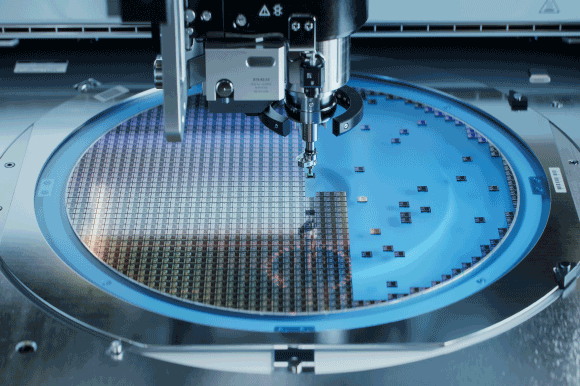

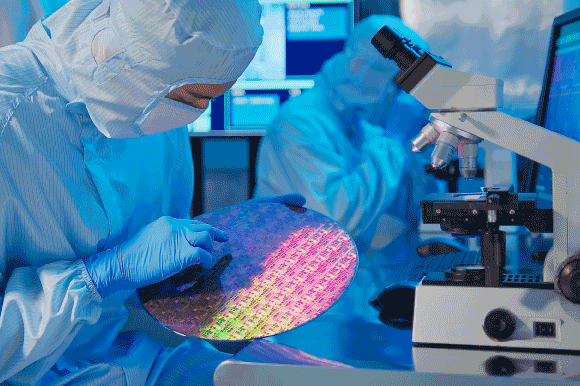

半導体ウェーハの外観検査まるわかりブック

【この資料で分かること】

- 多様なウェーハ材料

- ウェーハ製造工程と外観検査

- 欠陥の種類

- 検査技術のカテゴリ

【こんな方におすすめ】

Siウェーハ、化合物ウェーハ(SiC, GaN, LT/LN, InP), ガラスウェーハ等の検査に関心や課題をお持ちの方

半導体工場の現場DXガイドブック -設備の予知保全、品質監視-

【この資料で分かること】

- 半導体製造工程とDXの取組み

- 製造プロセス監視の作業自動化

- ウェーハ欠陥の原因調査

- 設備稼働監視作業の自動化

- 装置・設備・部品の故障予兆監視

【こんな方におすすめ】

ウェーハ製造工場や、デバイス製造工場のファシリティ設備の業務課題に関心や課題をお持ちの方

OTを止めるな!!半導体業界に必須のサイバー攻撃対策

【この資料で分かること】

- 外部脅威を排除しセキュアな工場へ

- 内部関係者によるリスク対策

- サプライチェーンリスク

- 横感染

- リスク発生&対策ソリューションマップ

【こんな方におすすめ】

半導体製造工場の現場、IT担当者、半導体装置メーカーでセキュリティに関心と課題をお持ちの方

用語集

*¹ メタルトラック:メタルトラックとは、ICの金属配線層のことです。配線層の中で、一定の幅とピッチで平行に走る金属の線やスペースのことを指します。

*² セルハイト:セルハイトとは、スタンダードセルの物理的な高さを指すもので、主に配線トラックの数とそのピッチに関連して定義されます。例えば、セルが8トラックの高さを持つ場合、それは「8トラックハイトのセル」と呼ばれます

*³ IRドロップ:IRドロップとは、電流が抵抗を流れる際に生じる電圧降下を指します。

具体的には、高電流がVDD(電源)やGND(グラウンド)の配線を通る際、その配線の抵抗によって電圧降下(IRドロップ)が生じます。この電圧降下が大きいと、トランジスタの動作電圧が低下し、チップ全体の動作速度や信号のタイミングが影響を受ける可能性があります。

*⁴ 短チャンネル効果:短チャンネル効果とは、MOSFET(Metal-Oxide-Semiconductor Field-Effect Transistor)のようなフィールド効果トランジスタのゲート長が短縮するにつれて現れる一連の不都合な現象を指します。

特に、集積度を高めるためにトランジスタのサイズを縮小する現代の半導体プロセス技術において、短チャンネル効果は大きな問題となります。

例えば、トランジスタのゲート長が短くなると、ゲートがソース-ドレイン間のチャンネルを制御する能力が低下し、その結果、トランジスタをオンにするためのしきい値電圧が低下し、しきい値電圧付近での電流の急激な増加が発生し、トランジスタのスイッチング特性が劣化します。

*⁵ スタンダードセル:セルは、ひとつまたは複数のトランジスタから構成される、特定のロジック機能(例:ANDゲート、フリップフロップなど)を持つモジュールやブロックのことを指します。スタンダードセルとは、高さと横幅が標準化されているセルです。

*⁶ BSPDN:Backside Power Delivery Networkの略で、集積回路の裏側(backside)から電源を供給するための技術です。

*⁷ ナノTSV:ナノTSVとは非常に微細なサイズで製作された垂直方向に設置されたCu Viaで、同技術を用いて、BSPDNとBPRを接続する検討が行われています。