- HOME

- 【注目】AI時代の発展を支える半導体製造技術 「PLP技術」とは

生産現場 計測・検査

【注目】AI時代の発展を支える半導体製造技術

「PLP技術」とは

先端半導体の技術の中でも微細化と並んで今後の半導体性能を大きく左右する、3次元実装技術。その構成技術のであるPLP技術について解説します。

半導体製造現場の課題を解決!厳選ホワイトペーパー4選(無料)

PLP技術とは

PLP(Panel level package)とは、FOWLP(Fan out wafer level package)で量産採用された、チップの一括製造の考え方をパネルレベルでの製造に応用したものです。

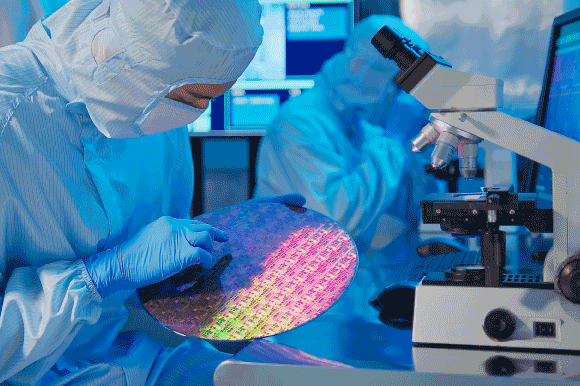

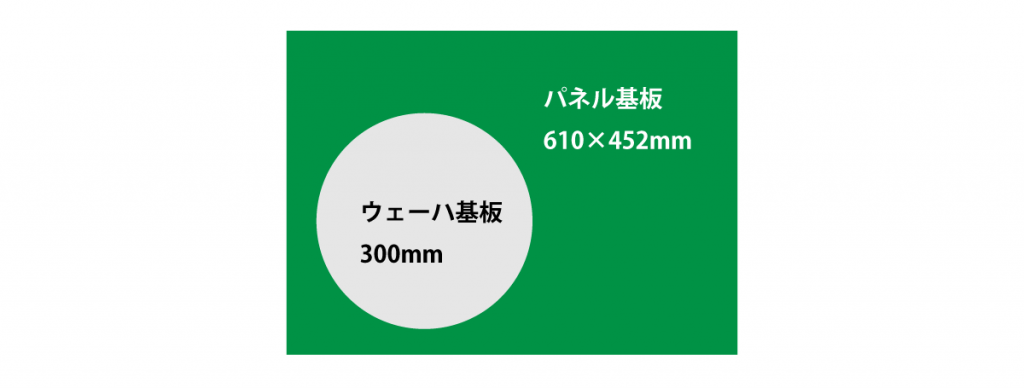

ウェハーレベルのFOWLPは、直径が300mmのウェハーに多数のシリコンダイを載せてパッケージの製造を一括して実施することで、パッケージ1個当たりの製造コストを低減する技術ですが、この一括製造の考え方を、ウェハーよりも大きなパネル(パネル状の基板)に適用したのが、パネルレベルのパッケージング技術です。パネルにはプリント基板*¹あるいはガラス基板が使用されています。

パネル基板の大きさは例えばプリント基板だと、610mm×457mmのため、この寸法と仮定して面積を比較してみると、300mmウェーハの面積が約707mm²であるのに対し、610mm×457mmの基板は約4倍の面積約2788mm²となります。

つまり、単純計算では、4倍の数のパッケージを一括して製造できることになるます。またチップ形状が四角のため、ウェーハ形状の基板に対して、より無駄がなくチップを配列することが可能です。

PLPもFOWLPと同様にチップ端子接続のためにRDL層を使用しますが、FOWLPのRDL層のL/Sが5um以下に対して、PLPのL/Sは10um以上とFOWLPほどRDL層の微細配線形成ができません。

この理由としては、基板サイズが大きいため基板の熱膨張の影響を受けやすく、大きな面積にわたって均一なRDL層を形成するのが難しいためです。そのため、PLPはピン数がそれほど多くないレガシー半導体のパッケージングに現在は主に使用されています。

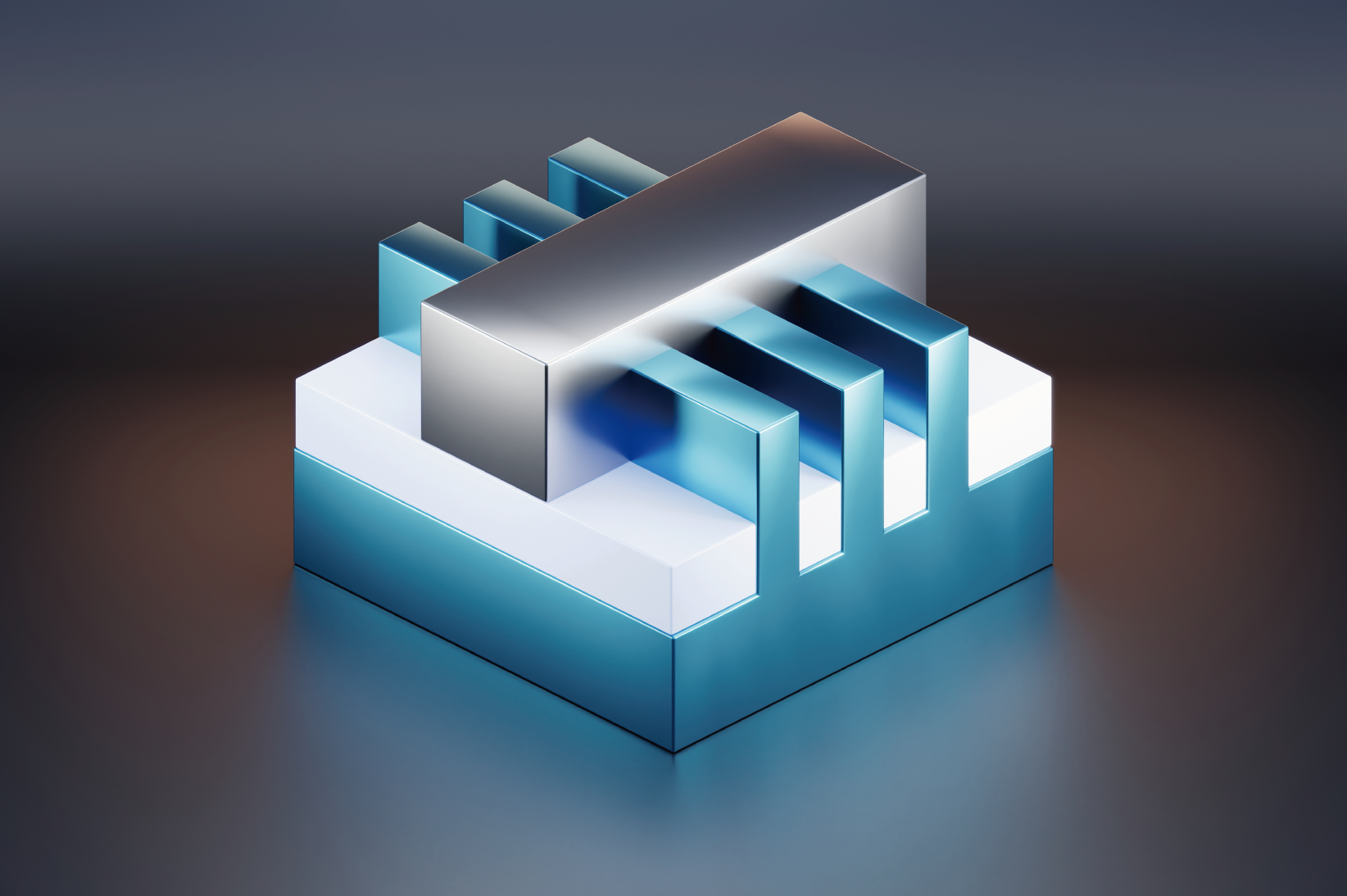

ウェーハ基板、パネル基板 サイズ比較イメージ

PLP製作工程

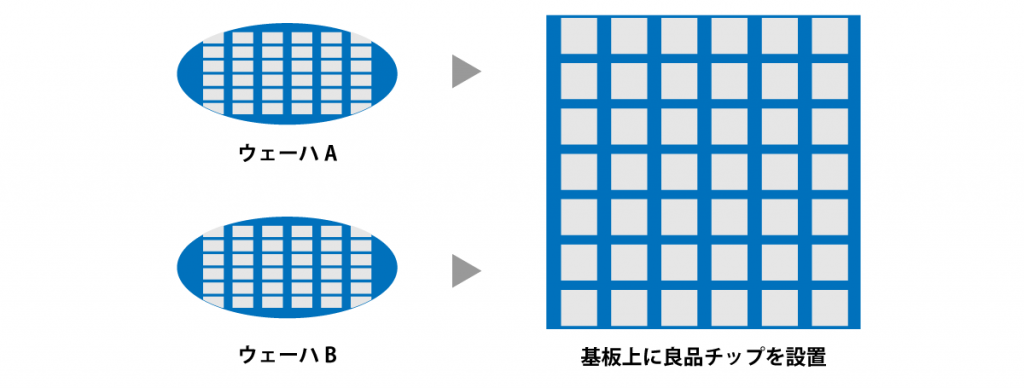

PLPの製造工程は、まずダイシングリング状のウェーハの良品をピックアップし、パネル基板の所定位置に設置することから始まります。これをPick & Place 工程と呼びます。設置する基板上にRDLを形成するには、主に2つの工程があります。ただし、それぞれの工程でRDLを形成するタイミングが異なります。

1つ目はチップを基板上に設置した後にRDLを形成する方式で、MOLOD樹脂*²でチップを封止してからRDL層を形成するため、こちらはMOLD Firstプロセスと呼ばれています。

2つ目はチップを基板上に設置する前にRDLを形成する方式で、パネル基板上にRDLを形成した後にチップを設置し、その後にMOLD樹脂でチップを封止するために、RDL Firstプロセスと呼ばれています。

MOLD Firstプロセスにおいては、チップの回路面をパネル基板方向に向けるか否かで2つの形成プロセスがあります。

チップ回路面をパネル基板方向に向ける製造工程をFACE DOWN方式、それとは反対の向きをFACE UP方式と呼んでいます。

以上のように、MOLD FirstとRDL Firstにはそれぞれメリットとデメリットがあります。どちらを採用するかは、チップの特性や製造プロセスなどを考慮した上で選択する必要があります。

Panel level package Pick and Place 工程

PLP技術の課題

PLP技術はFOWLPに比べて、より多くのチップの一括製造ができるため、コストを抑えることができるメリットがありますが、課題としては、新しい工程のためにパネルのサイズを含めた標準化がまだできていない点があげられます。また大型パネルを加工するための装置およびプロセスもまだ開発途上になります。

また、ダイシフト(die shift)と呼ばれるパネル上に配置されたチップの位置が、設計上の位置からずれる現象も問題となります。ダイシフト要因としては、パネル上での熱膨張や加工時の微小な誤差などによるダイの位置ずれなど、さまざまな要因が考えられます。大型基板上のRDL層微細化が進めば、先端のデバイスにも対応できるようになり、より多くのアプリケーションに採用が進むと考えられています。

今後はEV車載向けなどでレガシー半導体でありながら高密度実装が必要とされるケースが予想されるため、PLPはさらなる半導体の多様化に貢献する技術として注目されています。

半導体製造現場の課題を解決!厳選ホワイトペーパー

半導体製造現場の「検査」「監視・調査」「セキュリティ」について、例を挙げて解説しています。日々の業務に是非ご活用ください。

半導体は次の次元へ 微細化から集積へ アドバンストパッケージの世界

【この資料で分かること】

- 市場と技術の未来

- アドバンストパッケージの進化

- ウェーハ加工の課題解決

【こんな方におすすめ】

半導体市場やアドバンストパッケージ技術の動向を把握したい方、製造工程やウェーハ加工における課題解決を求めている方、高速化・高密度化を実現する製造技術に興味がある方、次世代半導体の開発に関わる技術者やエンジニアの方

半導体ウェーハの外観検査まるわかりブック

【この資料で分かること】

- 多様なウェーハ材料

- ウェーハ製造工程と外観検査

- 欠陥の種類

- 検査技術のカテゴリ

【こんな方におすすめ】

Siウェーハ、化合物ウェーハ(SiC, GaN, LT/LN, InP), ガラスウェーハ等の検査に関心や課題をお持ちの方

半導体工場の現場DXガイドブック -設備の予知保全、品質監視-

【この資料で分かること】

- 半導体製造工程とDXの取組み

- 製造プロセス監視の作業自動化

- ウェーハ欠陥の原因調査

- 設備稼働監視作業の自動化

- 装置・設備・部品の故障予兆監視

【こんな方におすすめ】

ウェーハ製造工場や、デバイス製造工場のファシリティ設備の業務課題に関心や課題をお持ちの方

OTを止めるな!!半導体業界に必須のサイバー攻撃対策

【この資料で分かること】

- 外部脅威を排除しセキュアな工場へ

- 内部関係者によるリスク対策

- サプライチェーンリスク

- 横感染

- リスク発生&対策ソリューションマップ

【こんな方におすすめ】

半導体製造工場の現場、IT担当者、半導体装置メーカーでセキュリティに関心と課題をお持ちの方

用語集

*¹ プリント基板:プリント基板とは、電気回路を構成するための基板のことです。プリント基板は、導電性の薄い金属箔を張った基板に、予め設計された回路パターンを印刷することによって作られます。

*² MOLD樹脂:MOLD樹脂は、半導体製造工程で使用される樹脂の一種です。MOLDとは、「Molded Plastic Package」の略称で、樹脂成形パッケージとも呼ばれます