- HOME

- 【注目】AI時代の発展を支える半導体製造技術 「TSV技術」とは

生産現場 計測・検査

【注目】AI時代の発展を支える半導体製造技術

「TSV技術」とは

TSV技術とは

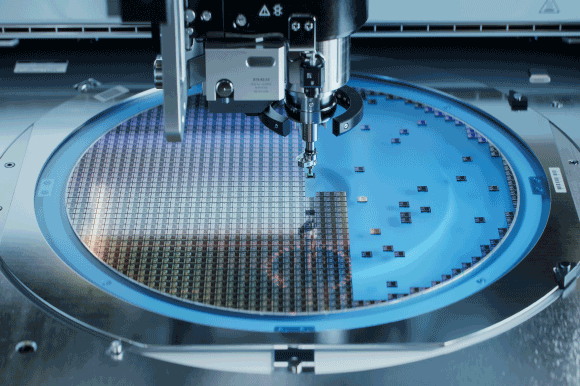

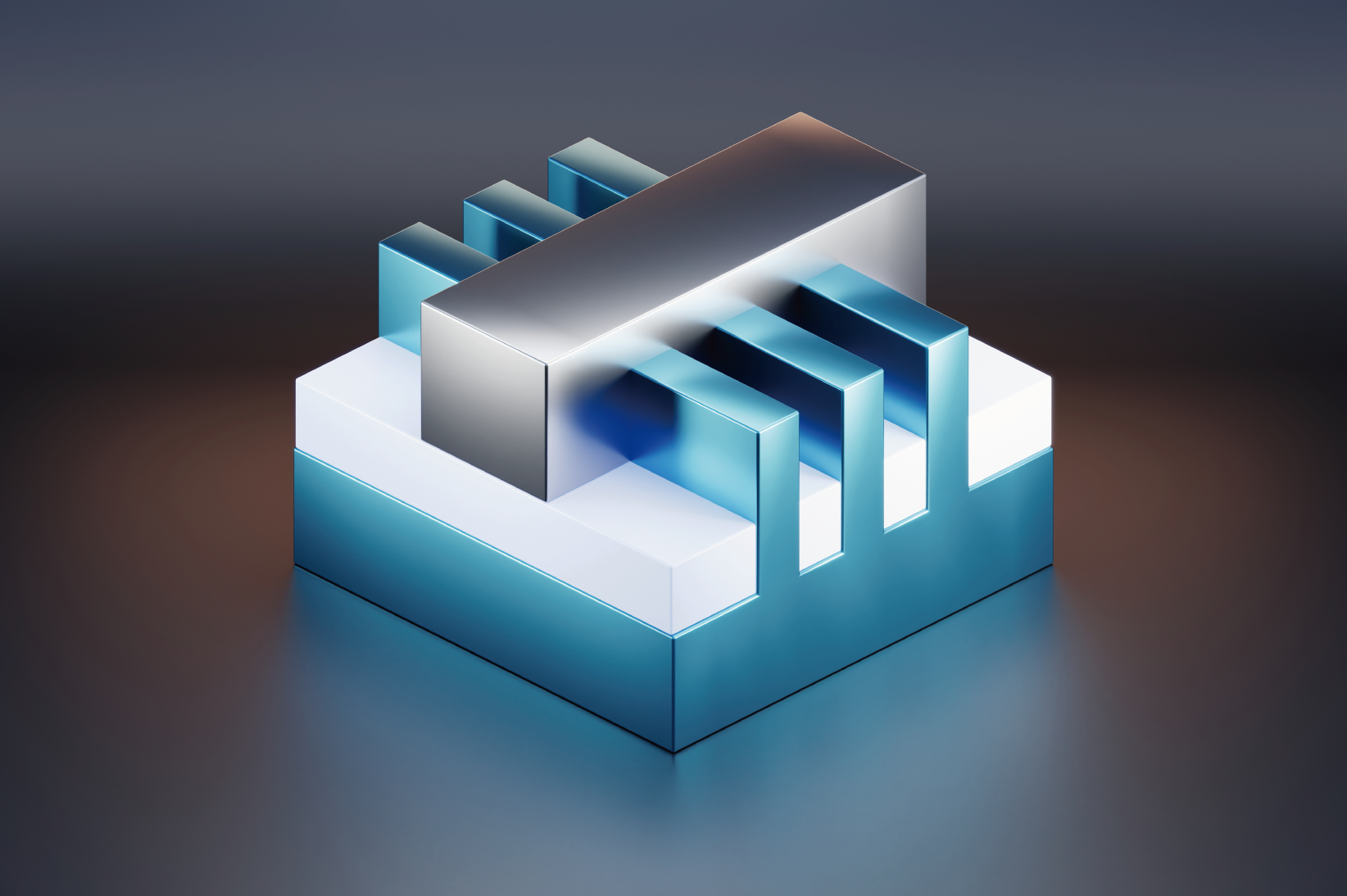

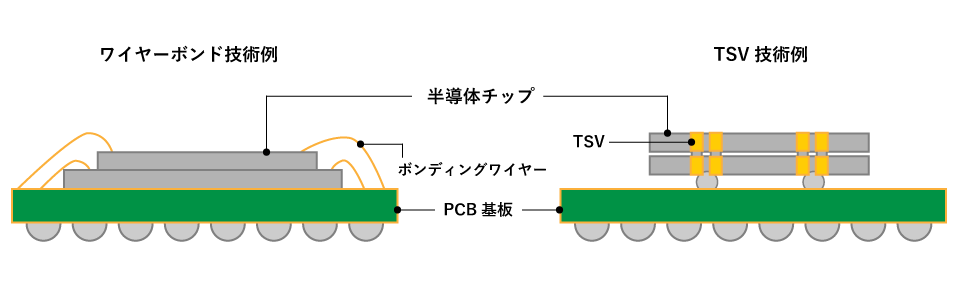

TSV(Through silicon via)技術とは、シリコン貫通電極の意味で、従来Cuワイヤーボンドにてチップを電気的に接続する代わりに、シリコンウェーハー内部に上下貫通する細い穴(ビア)をあけてその内側に金属を埋め込んで電極を作成し、マイクロバンプを通してシリコンチップを電気的かつ機械的に接続する技術です。

TSVのメリットとしては、主に以下3つがあります。

・処理速度の高速化:TSVを使用することで、ワイヤーボンドに比べてチップ間の距離を短縮することができます。これにより、高速で信号を伝送することができます。また多端子化への対応も可能になります。

・小型化/高密度化:TSVを使用することで、複数のチップを積層して1つのパッケージにすることができます。これにより、パッケージのサイズを小さくすることができます。またワイヤーボンドに比べて横に張り出すワイヤーがないので、面積を縮小できます。

・低消費電力:TSVを使用することで、信号伝送距離を短縮することができます。これにより、配線抵抗が減少し、消費電力を低減することができます。

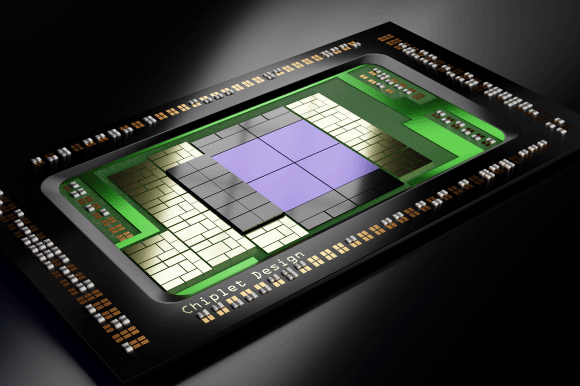

TSV技術は現在主に、積層型イメージセンサー、HBM(High band width memory)、シリコンインターポーザーなどで使用されています。将来的には異種チップを垂直に接続する3DICを実現する技術として期待されています。

ワイヤーボンドとTSVの違い

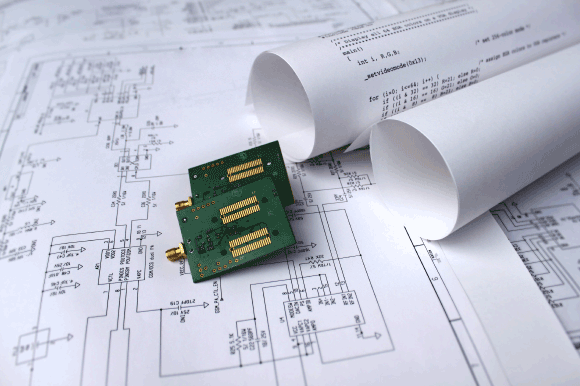

TSV製作工程の種類

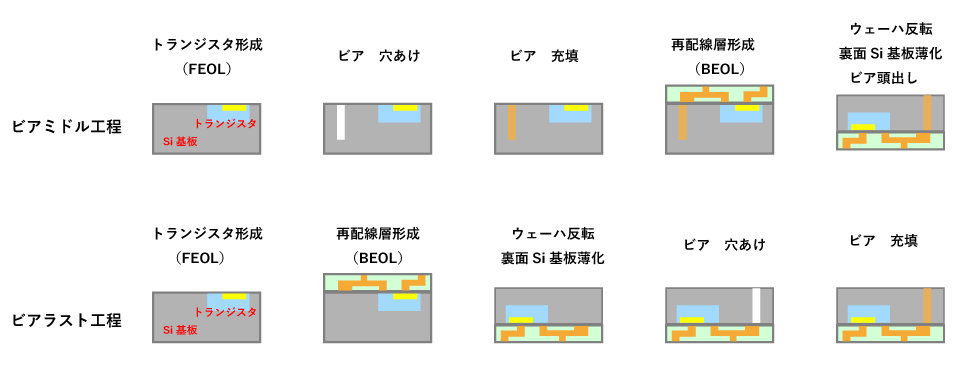

TSVのビア製作の種類は複数種類あり、現在ではビアミドルプロセスとビアラストプロセスが主流となっています。

ビアミドルプロセスについては、BEOL*¹と呼ばれる配線工程の途中でビア作成を行うプロセスで主に、作成のために前工程のウェーハプロセスを用いるため、ファンドリー*²などの前工程メーカーで行われているプロセスです。

ビアラストプロセスはFEOL*³とBEOLの全ての配線を完了したウェーハに、サポートをつけてウェーハを薄化したあとにビアを作成するプロセスです。完成ウェーハに対して、薄化、ビア作成を行うため主にOSAT*⁴などの後工程の専業メーカで実施されているプロセスです。

各ビアの製作工程

TSV技術の課題

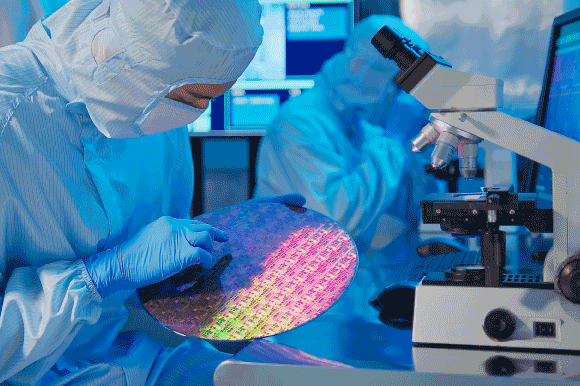

従来ワイヤーボンド技術に比べて、TSV技術とマイクロバンプ技術は比較的新しく、製造が複雑なため、製造コストが高い問題があります。

例えば製造コストでいうと、穴あけのためエッチングが必要でさらにSiとCuを絶縁するために絶縁膜の形成も必要となります。材料的なコストも高額になります。

プロセス側の問題としては、熱膨張率の違いによる応力の問題があります。TSVはCu電極の穴を形成するために、Si基板をなるべく薄化するのが望ましく(例50um等)そのためチップ内部に残留応力がやすく、チップ内部の異なる層の熱膨張率が異なる場合、応力が集中し、チップの欠陥や割れが発生する可能性があります。

また、技術的には量産されてからまだ歴史が短く、現在は使用されているデバイスが限られているため長期的な信頼性の問題もあります。

例えば、TSVがチップ内部を貫通することにより、チップの電気的特性が影響を受けて、インダクタンスやキャパシタンスが増加することにより、信号の遅延や減衰が発生する可能性があります。

また、TSVを作成するうえで使用する材料、プロセスが長期的には、絶縁層の劣化を引き起こし、チップの信頼性が低下する可能性があります。

このような問題はありますが、今後の半導体のさらなる高速化、高集積化、低電力化の実現ためにはTSV技術を利用した3次元積層技術の重要性はますます高まるため、デバイスメーカー、材料メーカー、装置メーカーが共同で解決に向けて取り組んでいます。

半導体製造現場の課題を解決!厳選ホワイトペーパー

半導体製造現場の「検査」「監視・調査」「セキュリティ」について、例を挙げて解説しています。日々の業務に是非ご活用ください。

半導体は次の次元へ 微細化から集積へ アドバンストパッケージの世界

【この資料で分かること】

- 市場と技術の未来

- アドバンストパッケージの進化

- ウェーハ加工の課題解決

【こんな方におすすめ】

半導体市場やアドバンストパッケージ技術の動向を把握したい方、製造工程やウェーハ加工における課題解決を求めている方、高速化・高密度化を実現する製造技術に興味がある方、次世代半導体の開発に関わる技術者やエンジニアの方

半導体ウェーハの外観検査まるわかりブック

【この資料で分かること】

- 多様なウェーハ材料

- ウェーハ製造工程と外観検査

- 欠陥の種類

- 検査技術のカテゴリ

【こんな方におすすめ】

Siウェーハ、化合物ウェーハ(SiC, GaN, LT/LN, InP), ガラスウェーハ等の検査に関心や課題をお持ちの方

半導体工場の現場DXガイドブック -設備の予知保全、品質監視-

【この資料で分かること】

- 半導体製造工程とDXの取組み

- 製造プロセス監視の作業自動化

- ウェーハ欠陥の原因調査

- 設備稼働監視作業の自動化

- 装置・設備・部品の故障予兆監視

【こんな方におすすめ】

ウェーハ製造工場や、デバイス製造工場のファシリティ設備の業務課題に関心や課題をお持ちの方

OTを止めるな!!半導体業界に必須のサイバー攻撃対策

【この資料で分かること】

- 外部脅威を排除しセキュアな工場へ

- 内部関係者によるリスク対策

- サプライチェーンリスク

- 横感染

- リスク発生&対策ソリューションマップ

【こんな方におすすめ】

半導体製造工場の現場、IT担当者、半導体装置メーカーでセキュリティに関心と課題をお持ちの方

用語集

*¹ BEOL: BEOLとは、「Back-end-of-line」の略語で、半導体製造工程の後半部分を指します。半導体の作成において、ウェハーに各種の回路を形成した後、その上に半導体デバイスを外部接続するための配線や保護層を形成するための工程です。

*² ファンドリー:ファンドリーとは半導体の製造に特化したサービスを提供する企業のことを指します。自社で半導体製造設備をもたないファブレス企業の設計図面に基づいて半導体回路の製造を行います。

*³ FEOL:FEOLとは、「Front-end-of-line」の略語で、半導体の製造工程の前半部分を指します。実際の半導体トランジスターを形成する工程になります。

*⁴ OSAT (Outsourced Semiconductor Assembly and Test):半導体のOSAT(Outsourced Semiconductor Assembly and Test)とは、半導体製品のアセンブリ(組み立て)やテストを受託するサービス企業のことを指します。前述のファンドリー企業がウェハーの製造を担当し、OSATがデバイスのアセンブリとテストを担当することが一般的です。