- HOME

- 【注目】 AI時代の発展を支える半導体製造技術 「Collective Die to Wafer Hybrid Bonding」とは

生産現場 計測・検査

【注目】 AI時代の発展を支える半導体製造技術

「Collective Die to Wafer Hybrid Bonding」とは

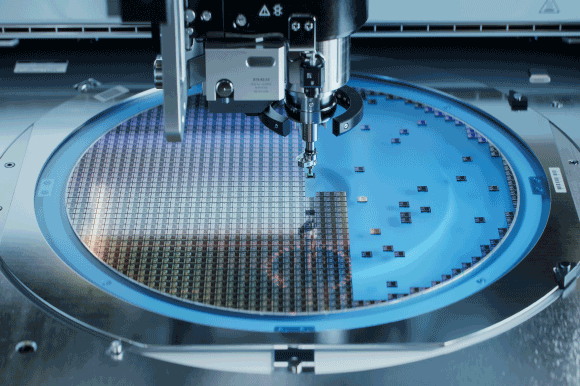

先端半導体の技術の中でも微細化と並んで今後の半導体性能を大きく左右する、3次元実装技術。その構成技術のであるCollective Die to Wafer Hybrid Bondingについて解説します。

半導体製造現場の課題を解決!厳選ホワイトペーパー4選(無料)

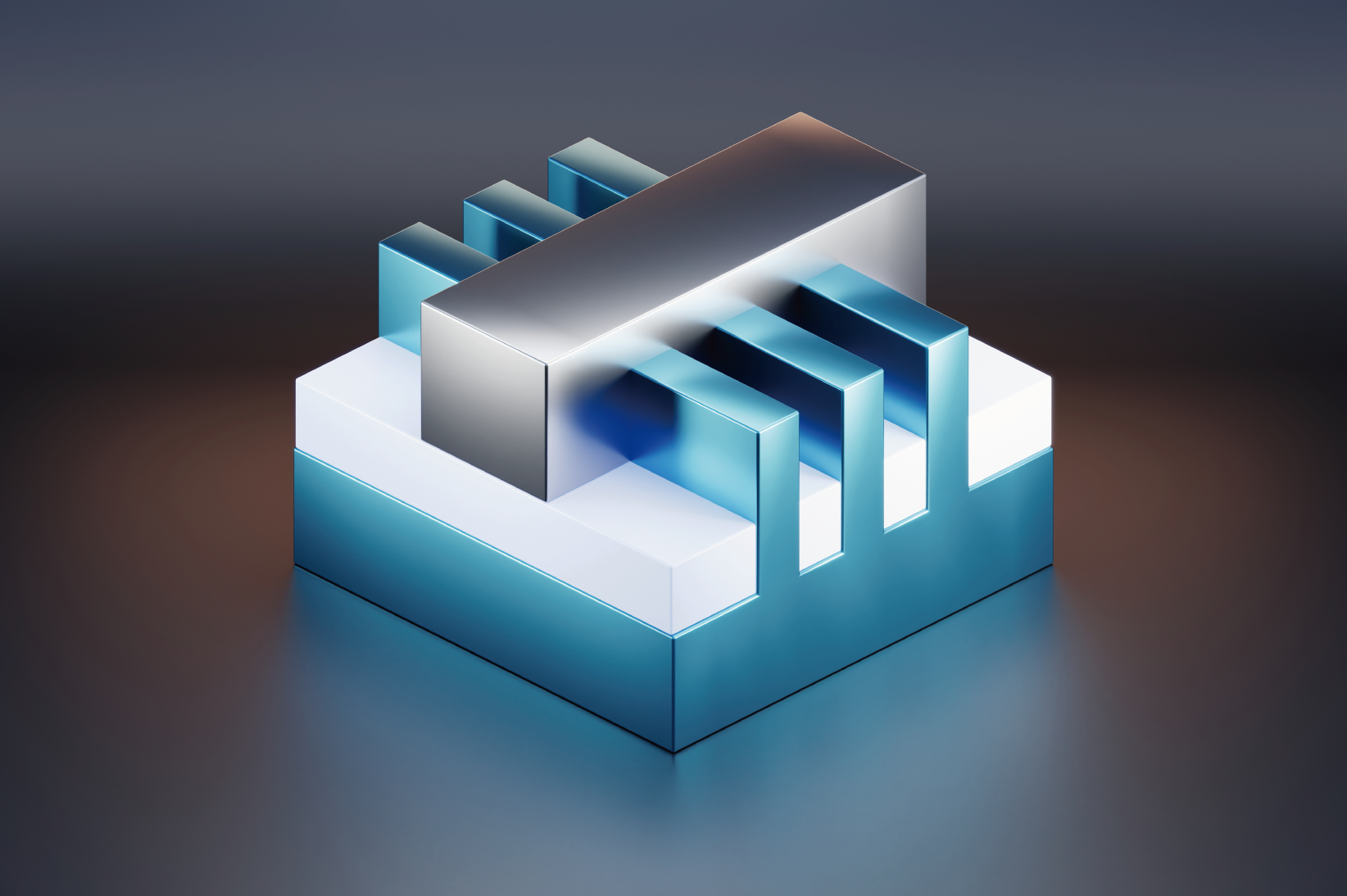

Collective Die to Wafer Hybrid Bondingとは

Collective Die to Wafer Hybrid Bondingとは2つ以上の半導体デバイスを垂直方向に高密度積層する際に使用されるHybrid bonding技術で、今後の半導体のキーテクノロジーであるヘテロジーニアスインテグレーション*¹ を実現するために採用が期待される技術の一つです。

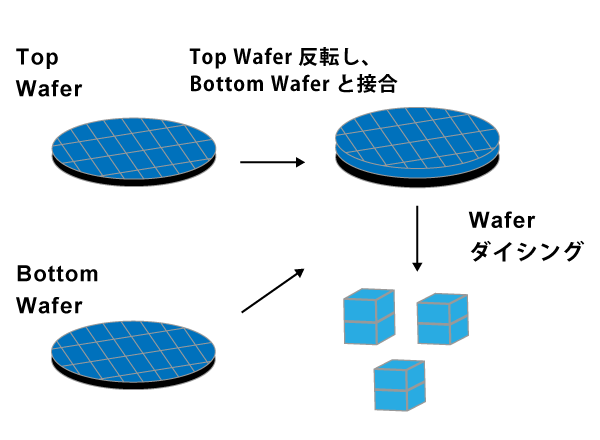

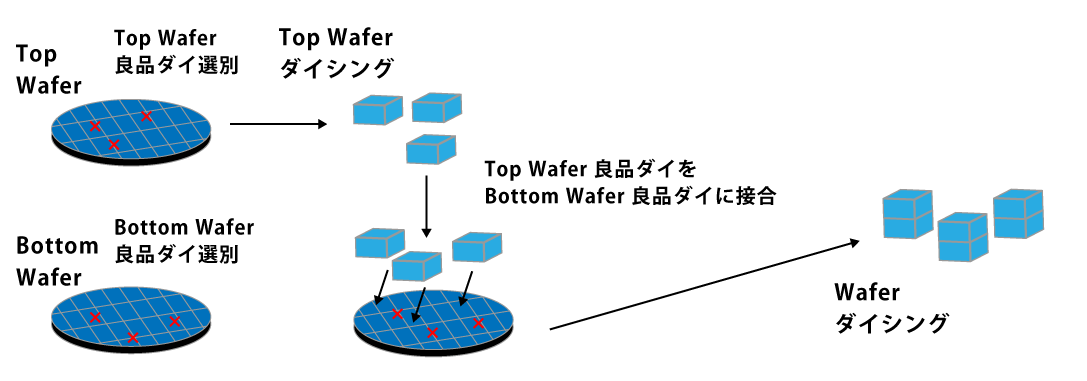

従来のHybrid bonding技術にはWafer同士を接合するWafer to Wafer接合技術とダイシングしたWafer ChipをWafer基板に接続するDie to Wafer接合技術の2つが採用されてきました。

Wafer to Wafer接合は一括で接合するために生産性は高いですが、高いアライメント精度が要求されるため歩留まりに問題があり、Die to Wafer接合は直接良品DieをWaferに接合するためにアライメント精度が高く歩留まりは高いですが、生産性がWafer to Wafer接合より劣るという課題がありました。

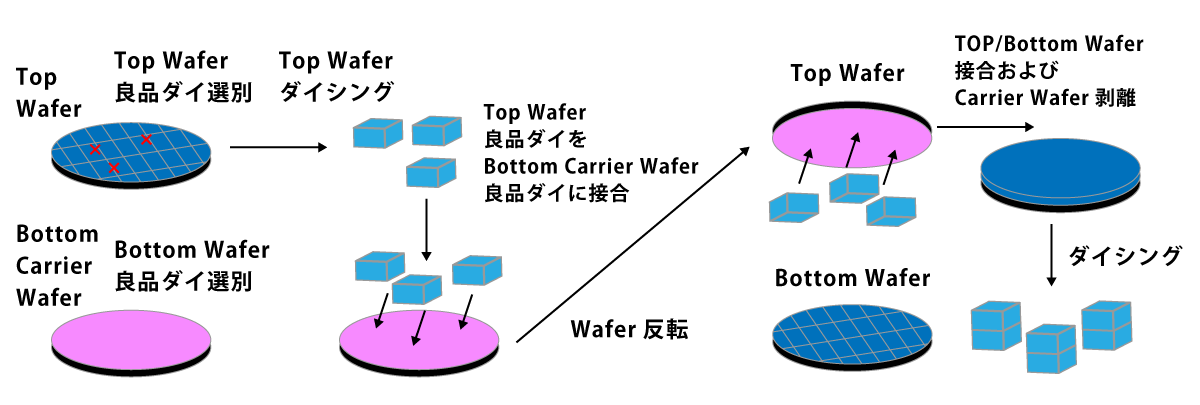

Collective Die to Wafer Hybrid Bondingは良品DieをキャリアWaferに接合したあとに、一括で接合するために従来のHybrid bondingの課題であった生産性と歩留まりの改善を実現する技術として注目されています。

Wafer to Wafer 積層

Die to Wafer 積層

Collective Die to Wafer 積層

Collective Die to Wafer Hybrid Bonding採用の背景

Collective Die to Wafer Hybrid Bonding採用の背景はAIアプリケーション向けにチップレット*² などの異種チップ接合デバイスの生産量が増加し、高精度かつ高生産の対応が可能な接合技術が必要とされてきている背景があります。

具体的には、Collective Die to Wafer Hybrid Bondingを採用する以下メリットがあります。

- 高密度インテグレーションの需要増加への対応

デバイスが小型化し、より高性能化するにつれて、高密度のチップインテグレーションへの需要が高まっています。Collective Die to Wafer Hybrid Bondingは、限られたスペースに複数の機能を統合する能力があるため、この需要に応えることができます。 - 製造効率の向上への対応

Collective Die to Wafer Hybrid Bonding技術は、一括でダイを接合するため、ダイを一つずつ接合する従来のDie to Wafer接合方法よりもスループットを向上させることができます。これにより、生産効率が向上し、コスト削減につながる可能性があります。 - 多様なチップの統合への対応

異なる種類のチップ(例えば、メモリ、ロジック、センサー)を1つのウェハーに統合することが可能です。これは、特に多機能性が求められるスマートフォンやIoTデバイスなどで性能向上に寄与します。 - システム性能向上への対応

ダイ間の距離が短縮されるため、信号伝送速度が向上し、エネルギー効率が良くなります。これは、高性能コンピューティングやデータセンターのアプリケーションで特に重要です。

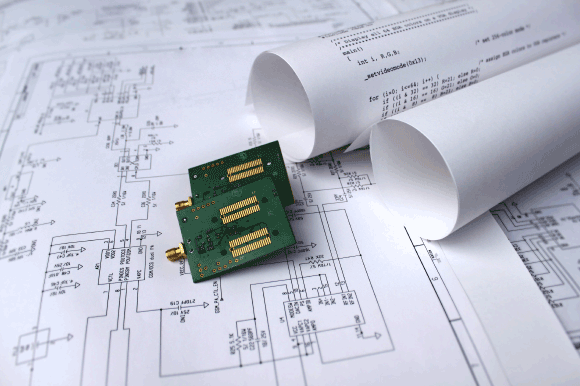

精密な位置決め技術、接合技術、検査技術の進歩により、Collective Die to Wafer Hybrid Bondingはより実現可能で信頼性の高いオプションとなっています。

Collective Die to Wafer Hybrid Bondingの課題と展望

Collective Die to Wafer Hybrid Bonding技術は、半導体業界において重要な進歩を遂げていますが、いくつかの課題に直面してます。具体的には以下があります。

- アライメントと精度

高度なアライメント精度が必要で、特に小さなダイサイズでの精度維持は難しいです。不正確なアライメントは性能の低下や欠陥を引き起こす可能性があります。 - 接合品質の一貫性

多数のダイを同時に接合する際に均一な接合品質を維持することは技術的難度が高く、品質の不均一性は信頼性に影響を及ぼす可能性があります。 - 熱管理

異なる素材の熱膨張率の違いが、接合中やデバイスの動作中に問題を引き起こす可能性があります。 - スケーリングとコスト

初期設備投資が高く、プロセスのスケーリングにはコストがかかるため、大量生産への適用の課題があります。 - 欠陥管理と検査

複数のダイの接合により、一つのダイの欠陥が全体に影響を及ぼす可能性があり、厳密な品質検査が必要です。

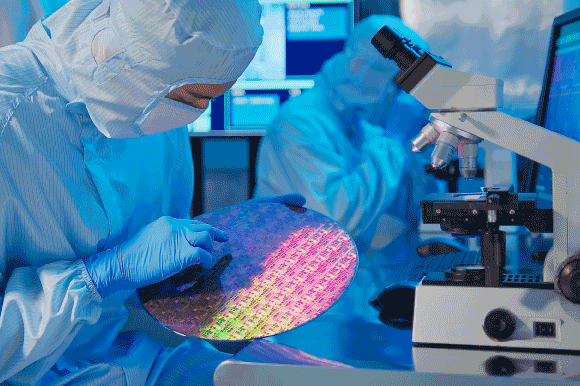

上記課題はありますが、Collective Die to Wafer Hybrid Bondingは、その高度なインテグレーション能力と効率性により、今後も半導体業界において重要な役割を果たすと予想されます。課題を克服し、技術の成熟を進めることで、この技術はより幅広いアプリケーションでの利用が見込まれます。

半導体製造現場の課題を解決!厳選ホワイトペーパー

半導体製造現場の「検査」「監視・調査」「セキュリティ」について、例を挙げて解説しています。日々の業務に是非ご活用ください。

半導体は次の次元へ 微細化から集積へ アドバンストパッケージの世界

【この資料で分かること】

- 市場と技術の未来

- アドバンストパッケージの進化

- ウェーハ加工の課題解決

【こんな方におすすめ】

半導体市場やアドバンストパッケージ技術の動向を把握したい方、製造工程やウェーハ加工における課題解決を求めている方、高速化・高密度化を実現する製造技術に興味がある方、次世代半導体の開発に関わる技術者やエンジニアの方

半導体ウェーハの外観検査まるわかりブック

【この資料で分かること】

- 多様なウェーハ材料

- ウェーハ製造工程と外観検査

- 欠陥の種類

- 検査技術のカテゴリ

【こんな方におすすめ】

Siウェーハ、化合物ウェーハ(SiC, GaN, LT/LN, InP), ガラスウェーハ等の検査に関心や課題をお持ちの方

半導体工場の現場DXガイドブック -設備の予知保全、品質監視-

【この資料で分かること】

- 半導体製造工程とDXの取組み

- 製造プロセス監視の作業自動化

- ウェーハ欠陥の原因調査

- 設備稼働監視作業の自動化

- 装置・設備・部品の故障予兆監視

【こんな方におすすめ】

ウェーハ製造工場や、デバイス製造工場のファシリティ設備の業務課題に関心や課題をお持ちの方

OTを止めるな!!半導体業界に必須のサイバー攻撃対策

【この資料で分かること】

- 外部脅威を排除しセキュアな工場へ

- 内部関係者によるリスク対策

- サプライチェーンリスク

- 横感染

- リスク発生&対策ソリューションマップ

【こんな方におすすめ】

半導体製造工場の現場、IT担当者、半導体装置メーカーでセキュリティに関心と課題をお持ちの方

- *¹ ヘテロジーニアスインテグレーション

- ヘテロジーニアスインテグレーションとは、異なる種類の材料、技術、デバイスを単一のシステムに統合する技術のことです。このアプローチは、異なる機能や特性を持つ複数のコンポーネントを組み合わせることで、単一の材料や技術では実現できない性能や機能を持つシステムを作り出します。

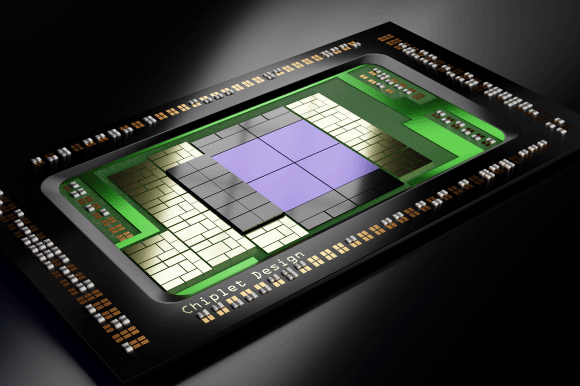

- *² チップレット

- 従来モノリシック製法で1チップ上に多機能デバイスを製造統合していたものをデバイスを機能毎に分割(チップレット化)したのちに再度別基板上で水平方向もしくは、垂直方向につなぎ合わせてて分割前と同様の機能を持つモジュールに統合する手法です。