- HOME

- 【注目】 AI時代の発展を支える半導体製造技術 「RDLインターポーザー」とは

生産現場 計測・検査

【注目】 AI時代の発展を支える半導体製造技術

「RDLインターポーザー」とは

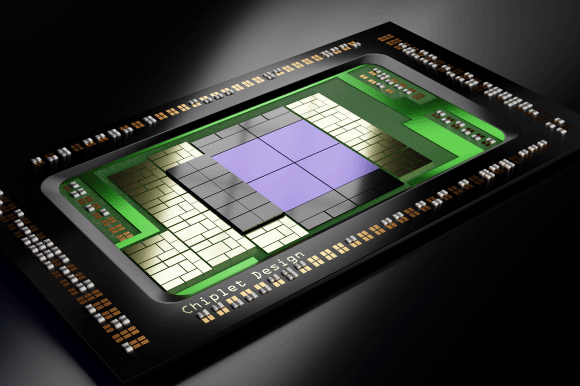

先端半導体の技術の中でも微細化と並んで今後の半導体性能を大きく左右する、3次元実装技術。その構成技術のであるRDLインターポーザーについて解説します。

半導体製造現場の課題を解決!厳選ホワイトペーパー4選(無料)

RDLインターポーザーについて

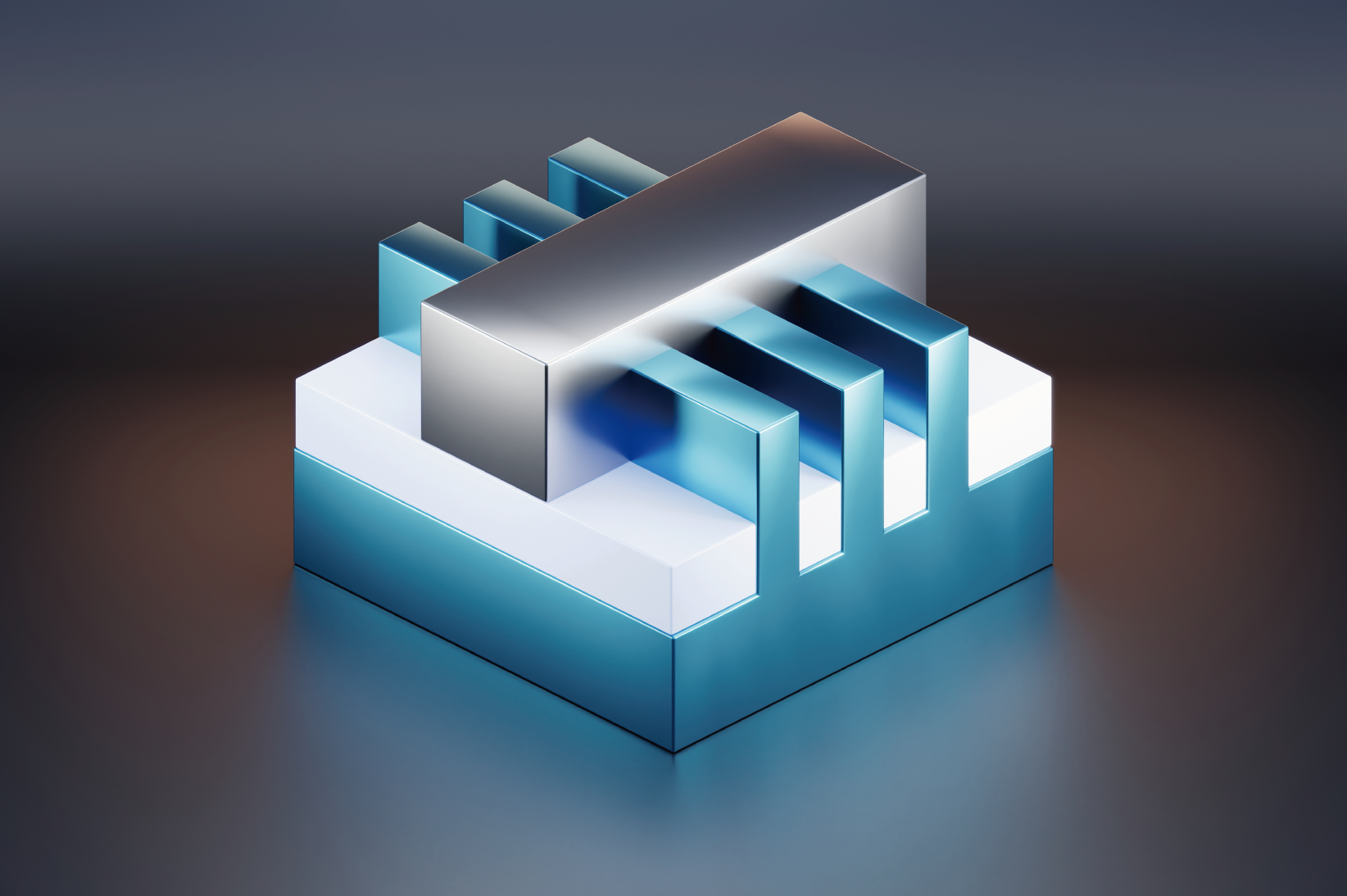

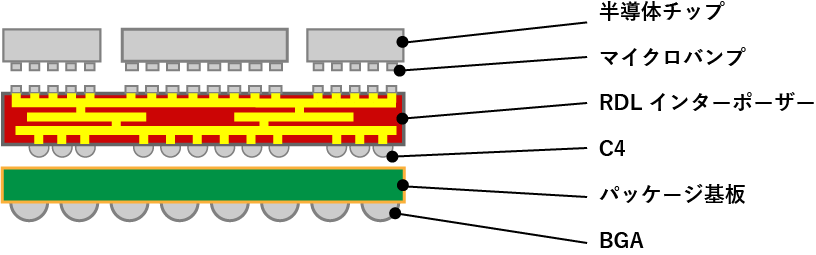

RDLインターポーザー(Redistribution Layer Interposer)とは、半導体製造における先端パッケージング技術*¹ の一つであるインターポーザ―基板を使用した2.5D実装の1種です。

具体的には樹脂基板上に、配線を再分配するための層(Redistribution Layer)を形成し、その上にチップレット化されたダイを同一平面状に並べて相互接続するインターポーザー技術の一つです。

RDLインターポーザーの一番の特徴としては、製造コストがSiインターポーザーと比較して低いということがあげられます。樹脂基板を使用するため、コスト効率が高いためです。

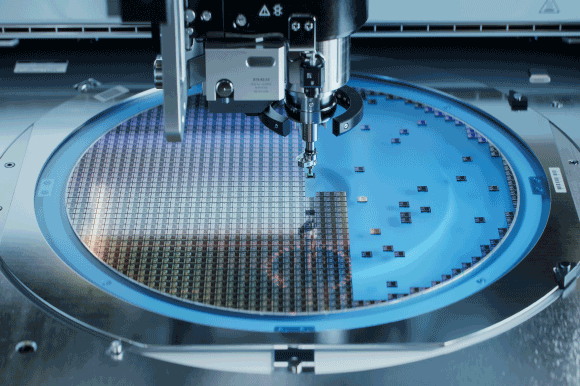

今現在インターポーザー基板を使った2.5D実装が使用されるAIやHPC向けの先端アプリケーション向けには、シリコン基板上にRDL配線をしたSiインターポーザーが主に使用されていますが、Siインターポーザーはウェーハ前工程プロセスで製造されるため高価であり、そのコストがパッケージ全体のコストを押し上げる要因となっていました。

また、先端デバイスのさらなる高集積化とダイサイズの大型化により、Siインターポーザーはインターポーザーサイズ大型化による電気特性の劣化、インターポーザーの最大サイズが12インチサイズまでしか大型化できないなどの能力的な制約に直面しています。

そんな中Siインターポーザーより低いコストで生産でき、電気特性もよく、インターポーザーサイズをSiインターポーザーより大型化できるRDLインターポーザーの採用が、シリコンブリッジ技術*² を使用したパッケージ基板とともに一部アプリケーションにおいて進んでいます。

RDLインターポーザーのイメージ図

SiインターポーザーとRDLインターポーザーの比較

RDLインターポーザーとSiインターポーザーは、半導体パッケージング技術において重要な役割を果たすインターポーザー技術ですが、それぞれ異なる特性を持っています。主な特徴を以下に記します。

材料とコスト

Siインターポーザーはシリコンを基材としており、微細な配線加工が可能ですが、コストが高いというデメリットがあります。一方、RDLインターポーザーは樹脂基板を使用し、製造コストを抑えることができるため、コスト効率が求められる用途に適しています。

配線と電気特性

Siインターポーザーは、非常に微細な配線が可能であるため、高性能なデータ転送が可能です。しかし、電気損失が大きくなる傾向があります。RDLインターポーザーは、配線幅がやや広いものの、低い比誘電率により電気損失が少なく、高周波特性に優れています。

製造プロセス

Siインターポーザーは、半導体のウェハープロセスを利用して製造されるため、精密な加工が可能です。しかしながらSiインターポーザー作成のコストは高額になります。一方、RDLインターポーザーは、パッケージ工程の設備を使用するため、加工費用が安く済みます。

このように、SiインターポーザーとRDLインターポーザーは、それぞれ異なる特性を持ち、用途に応じて使い分けられています。高性能が求められる場合は、Siインターポーザーが適しており、コスト効率が重視される場合はRDLインターポーザーが選ばれることが多くなっています。

RDLインターポーザーとSiインターポーザーの比較

| 特徴 | Siインターポーザー | RDLインターポーザー |

|---|---|---|

| 主な材料 | シリコン | 樹脂基板 |

| 配線幅/間隔 | 1um以下の微細加工が可能 | 約2umほどでSiほど微細ではない |

| 電気特性 | 高い比誘電率*³(約12)、電気損失が大きい | 低い比誘電率(約3-4)、電気損失が小さく高周波特性に優れる |

| 製造コスト | 高い | 比較的低い |

| 製造プロセス | 半導体ウェーハプロセスを使用 | パッケージ工程の設備を使用 |

| 適用例 | 高性能コンピューティング、AI、5G通信機器 | スマートフォン、ウェアラブルデバイス、IoTデバイス |

| 用途 | 高性能が求められるアプリケーション | 小型デバイスやコスト効率が求められる製品 |

| 長所 | 優れた熱伝導性と高密度配線 | 設計の柔軟性と低コスト |

| 短所 | 製造コストが高く、製造難易度が高い | 機械的強度や熱伝導性が劣る場合がある |

RDLインターポーザーの課題と展望

RDLインターポーザー(Redistribution Layer Interposer)は、デバイスの小型化や高密度化に貢献する技術ですが、さらなる普及にはいくつかの課題があります。

熱管理の課題

高密度な集積により発熱が問題となることがあり、特に高性能プロセッサやGPUを搭載する際には、効率的な熱管理が必要となります。高熱伝導材料や3Dスタック技術の導入で、熱を効果的に散逸させる技術が進化すると期待されます。

コスト効率の向上

RDLインターポーザーは比較的低コストですが、さらにコスト削減が必要です。大量生産を行うコンシューマー向けデバイスやIoTデバイスでは、コスト効率が特に重要なため製造プロセスの最適化や新素材の導入により、コスト削減のさらなる低減が必要となります。

製造技術の複雑化

配線の微細化や多層化に伴い、製造技術が複雑化しています。これが製造コストの上昇や歩留まりの低下を招く可能性があります。新しいリソグラフィー技術やナノ加工技術の進展により、製造プロセスの精度と効率が向上し、製造コストの抑制が期待されます。

材料の信頼性と耐久性

柔軟な材料が使用されるRDLインターポーザーには、耐久性や信頼性に課題があります。特に過酷な環境での使用では、材料の劣化が問題となる可能性があります。高耐久素材の開発が進み、過酷な条件でも長期間の使用が可能なインターポーザーが期待されます。

市場と応用分野の拡大

モバイルやIoT市場で広く使われていますが、自動車や医療機器など、新しい分野への展開が求められています。高耐久性や高温耐性を持つ製品が開発され、新たな市場での採用が期待されています。RDLインターポーザーはデバイスの高密度実装を可能とする重要な技術ですが、熱管理、コスト効率、製造技術、材料の信頼性、市場拡大などの課題があります。

これらの課題に対処するための技術革新が進むことで、RDLインターポーザーはさらに多くの分野での採用が期待されます。

半導体製造現場の課題を解決!厳選ホワイトペーパー

半導体製造現場の「検査」「監視・調査」「セキュリティ」について、例を挙げて解説しています。日々の業務に是非ご活用ください。

半導体は次の次元へ 微細化から集積へ アドバンストパッケージの世界

【この資料で分かること】

- 市場と技術の未来

- アドバンストパッケージの進化

- ウェーハ加工の課題解決

【こんな方におすすめ】

半導体市場やアドバンストパッケージ技術の動向を把握したい方、製造工程やウェーハ加工における課題解決を求めている方、高速化・高密度化を実現する製造技術に興味がある方、次世代半導体の開発に関わる技術者やエンジニアの方

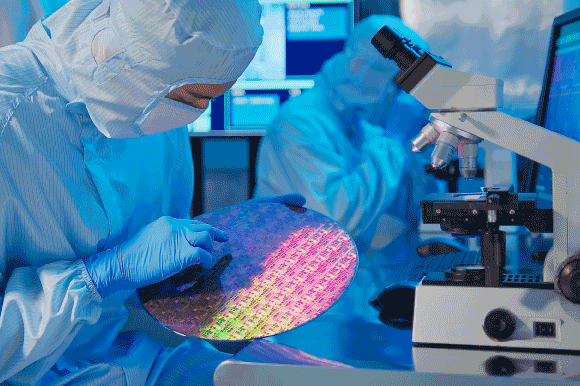

半導体ウェーハの外観検査まるわかりブック

【この資料で分かること】

- 多様なウェーハ材料

- ウェーハ製造工程と外観検査

- 欠陥の種類

- 検査技術のカテゴリ

【こんな方におすすめ】

Siウェーハ、化合物ウェーハ(SiC, GaN, LT/LN, InP), ガラスウェーハ等の検査に関心や課題をお持ちの方

半導体工場の現場DXガイドブック -設備の予知保全、品質監視-

【この資料で分かること】

- 半導体製造工程とDXの取組み

- 製造プロセス監視の作業自動化

- ウェーハ欠陥の原因調査

- 設備稼働監視作業の自動化

- 装置・設備・部品の故障予兆監視

【こんな方におすすめ】

ウェーハ製造工場や、デバイス製造工場のファシリティ設備の業務課題に関心や課題をお持ちの方

OTを止めるな!!半導体業界に必須のサイバー攻撃対策

【この資料で分かること】

- 外部脅威を排除しセキュアな工場へ

- 内部関係者によるリスク対策

- サプライチェーンリスク

- 横感染

- リスク発生&対策ソリューションマップ

【こんな方におすすめ】

半導体製造工場の現場、IT担当者、半導体装置メーカーでセキュリティに関心と課題をお持ちの方

用語集

- *¹ 先端パッケージ技術

- 先端パッケージ技術とは、半導体チップを高密度に集積し、性能や電力効率を向上させる技術です。3Dスタッキングやシステムインパッケージ(SiP)などの手法を活用し、デバイスの小型化や多機能化を実現します。

- *² Siブリッジ技術

- Siブリッジ技術とは、半導体チップ間をシリコン基板で接続する技術です。これにより、高密度かつ高性能な電気的接続が可能となり、チップレット間の信号伝送を最適化します。Siブリッジは、パッケージ内での配線距離を短縮し、システム全体の性能向上と電力効率の改善に貢献します。

- *³ 比誘電率

- 比誘電率とは、物質の誘電特性を示す無次元数値で、真空中の誘電率に対する物質の誘電率の比です。材料の電気的特性を評価する際に重要で、高い比誘電率は電場に対して大きな電気分極を引き起こし、コンデンサなどの電気部品の性能に影響を与えます。