- HOME

- 【注目】 AI時代の発展を支える半導体製造技術 「半導体IP」とは

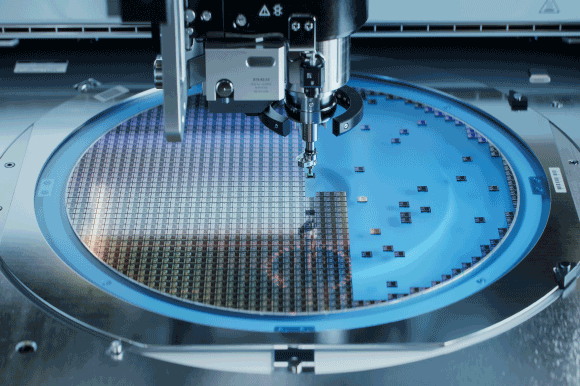

生産現場 計測・検査

【注目】 AI時代の発展を支える半導体製造技術

「半導体IP」とは

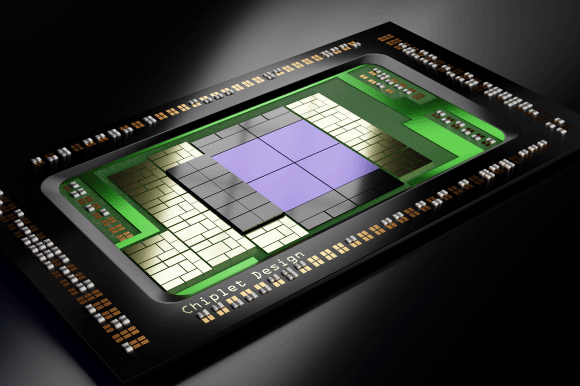

本シリーズで3次元実装技術について解説をしてまいりましたが、今回は番外編として、半導体エコシステムの一角を担う半導体IPについて解説します。チップ設計の効率化や製品化までのスピードアップ、そしてコスト削減に貢献するこの技術の秘密に迫ります。

半導体製造現場の課題を解決!厳選ホワイトペーパー4選(無料)

半導体IPとは

半導体業界における「IP(Intellectual Property: 知的財産)」は、特定の機能を果たすために設計された再利用可能な半導体設計ブロックのことを指します。

これらは、チップ設計の効率化を目的として、システムオンチップ(SoC)などの複雑な半導体製品の開発に広く使用されています。

半導体IPの利用が普及する前は、フルカスタム設計*¹ やスタンダードセル設計*² という手法で半導体が設計されていました。これらの手法では、各設計はゼロから開始され、再利用可能なコンポーネントは限定的でした。

そのため、設計に時間がかかり、納期およびコストが増えていくという問題がありました。

半導体IPを利用することにより、設計プロセスの初期段階から高度に最適化されたコンポーネントを利用できるため、設計から製品化までの時間を大幅に短縮することが可能になりました。

またIPの再利用により、新たな設計にかかるコストを削減し、研究開発や検証プロセスに要する投資を減らすことが可能となりました。

加えて、すでに市場で検証され、広く採用されているIPを使用することで、設計ミスや性能上の問題リスクを低減することもできるようになりました。

半導体設計手法の比較図

| フルカスタム設計 | スタンダードセル設計 | 半導体IPを使った設計 | |

|---|---|---|---|

| 特徴 | 最適化された回路を一から設計 | あらかじめ定義された機能ブロックを使用 | 既存の設計ブロックの再利用 |

| メリット | 最高の性能と最小の面積を実現 | 開発時間とコストの削減 | 開発の迅速化と設計リスクの低減 |

| デメリット | 開発に時間とコストがかかる | フルカスタムに比べて性能が劣る可能性 | ライセンス料が発生し、カスタマイズに限界 |

半導体エコシステムについて

半導体業界はもともとはIDM(Integrated Device Manufacturer)と呼ばれる設計から製造までを一貫して行うメーカーが主でありましたが、現在はチップ構成の複雑さや微細化の進展にともない分業が進んでいます。

具体的には、ファブレスと呼ばれる、自社で製造設備をもたない半導体の設計に特化したメーカーにてチップ設計を行い、それをファンドリーで製造、OSATでパッケージ実装する形となっています。

半導体IPは主にファブレス企業がチップ設計を行う際に用いられます。半導体ファブレス企業が半導体IPを利用するメリットには以下があります。

1. 開発期間の短縮

半導体IPを使用することで、ファブレス企業は設計プロセスを大幅に加速させることができます。

プリデザインされた、検証済みのIPコアを組み合わせることで、設計からプロトタイピング、製品化までの時間を短縮できるため、市場投入までの時間を大幅に削減できます。

2. コスト削減

設計から始める代わりに、既存のIPをライセンスすることで、研究開発費用を削減できます。

さらに、半導体IPは設計ミスを減らし、再設計の必要性を低減することで、全体的な開発コストを削減します。

3. リスクの低減

検証済みのIPコアを使用することで、設計プロセスにおけるリスクが低減します。

信頼性の高いIPを使用することで、設計不備による遅延や失敗のリスクを減らし、最終製品の品質と信頼性を向上させることができます。

4. 専門知識の活用

特定の技術分野や機能に特化したIPコアを利用することで、ファブレス企業はその分野の専門知識を活用できます。

これにより、企業は自社のコアコンピテンスに集中しつつ、製品の機能性と性能を向上させることができます。

5. 競争力の向上

高品質なIPコアを使用することで、ファブレス企業は競争力のある製品を迅速に市場に投入できます。また、IPを活用することで、最新の技術トレンドに迅速に対応し、製品ポートフォリオを拡大できます。

6. カスタマイズと拡張性

多くの半導体IPは、特定のアプリケーションや顧客のニーズに合わせてカスタマイズ可能です。これにより、ファブレス企業は幅広い市場や用途に対応する製品を効率的に開発できます。

7. 技術革新への貢献

最新の半導体IPを組み込むことで、ファブレス企業は技術革新を推進し、業界の進化に貢献できます。これにより、企業は市場でのリーダーシップを確立し、長期的な成長を促進することができます。

このように現代の先端半導体を製造する半導体エコシステムの確立に半導体IPは非常な重要な役割をしめています。

半導体エコシステムの比較表

| 企業タイプ | 特徴 | 設計 | 製造 | 実装 |

|---|---|---|---|---|

| IDM | 設計から製造、販売までを一貫して行う企業 製品の品質管理や技術の統一性が高いが、分業に比べコストがかかる |

○ | ○ | ○ |

| ファブレス | 半導体設計に特化した企業 | ○ | ||

| ファンドリー | 他社の設計に基づいて半導体製造サービスを提供する企業 | ○ | ||

| OSAT | 半導体の組み立て、パッケージング、テストを提供する企業 | ○ |

AI時代に必要とされる半導体IPとは

AI時代の半導体IPとしては、AIが使用されるアプリケーションの多様さに対応するための柔軟性、また持続可能性の観点から高い性能と同時に今まで以上に効率的な電力消費が必要となります。

そのためRISC-V*³ アーキテクチャーなどの新しいIPソリューションと従来のGPU、CPUなどのアーキテクチャーの融合が必要となってきています。

半導体IP業界は、AI技術の急速な進化に対応するため、これまで以上に継続的な研究開発と産業界・学界との協力が必要とされてきています。

これらの業種を超えた半導体エコシステム間の協業により、AI半導体の抱える消費電力、処理速度、柔軟性などの課題を克服し、AIの可能性を最大限に引き出すエコシステムの構築が期待されています。

半導体製造現場の課題を解決!厳選ホワイトペーパー

半導体製造現場の「検査」「監視・調査」「セキュリティ」について、例を挙げて解説しています。日々の業務に是非ご活用ください。

半導体は次の次元へ 微細化から集積へ アドバンストパッケージの世界

【この資料で分かること】

- 市場と技術の未来

- アドバンストパッケージの進化

- ウェーハ加工の課題解決

【こんな方におすすめ】

半導体市場やアドバンストパッケージ技術の動向を把握したい方、製造工程やウェーハ加工における課題解決を求めている方、高速化・高密度化を実現する製造技術に興味がある方、次世代半導体の開発に関わる技術者やエンジニアの方

半導体ウェーハの外観検査まるわかりブック

【この資料で分かること】

- 多様なウェーハ材料

- ウェーハ製造工程と外観検査

- 欠陥の種類

- 検査技術のカテゴリ

【こんな方におすすめ】

Siウェーハ、化合物ウェーハ(SiC, GaN, LT/LN, InP), ガラスウェーハ等の検査に関心や課題をお持ちの方

半導体工場の現場DXガイドブック -設備の予知保全、品質監視-

【この資料で分かること】

- 半導体製造工程とDXの取組み

- 製造プロセス監視の作業自動化

- ウェーハ欠陥の原因調査

- 設備稼働監視作業の自動化

- 装置・設備・部品の故障予兆監視

【こんな方におすすめ】

ウェーハ製造工場や、デバイス製造工場のファシリティ設備の業務課題に関心や課題をお持ちの方

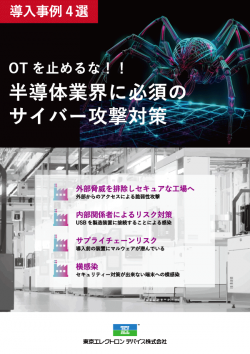

OTを止めるな!!半導体業界に必須のサイバー攻撃対策

【この資料で分かること】

- 外部脅威を排除しセキュアな工場へ

- 内部関係者によるリスク対策

- サプライチェーンリスク

- 横感染

- リスク発生&対策ソリューションマップ

【こんな方におすすめ】

半導体製造工場の現場、IT担当者、半導体装置メーカーでセキュリティに関心と課題をお持ちの方

- *¹ フルカスタム設計

- フルカスタム設計とは、、回路やレイアウトを特定のアプリケーションや性能要件に完全に合わせて一から設計する方法です。

- このアプローチでは、最大の柔軟性と最適化が可能であり、高性能や低消費電力などの特定の目標を達成するために用いられますが、時間とコストがかかります。

- *² スタンダートセル設計

- スタンダートセル設計とは、あらかじめ定義された機能ブロック(スタンダードセル)を組み合わせて半導体を設計する方法です。設計プロセスが効率化され、開発時間とコストを削減できますが、フルカスタム設計に比べると、最適化の度合いに制限があります。

- *³ RISC-V

- RISC-V(リスク・ファイブ)とは、オープンソースの命令セットアーキテクチャ(ISA)です。特徴として、オープンソース性とカスタマイズの自由度が、従来の商用ISAと比較してあり、より民主的で参加しやすいエコシステムを提供し、新たな技術革新の可能性を広げています。