- HOME

- 【注目】 AI時代の発展を支える半導体製造技術 「シリコンブリッジ技術」とは

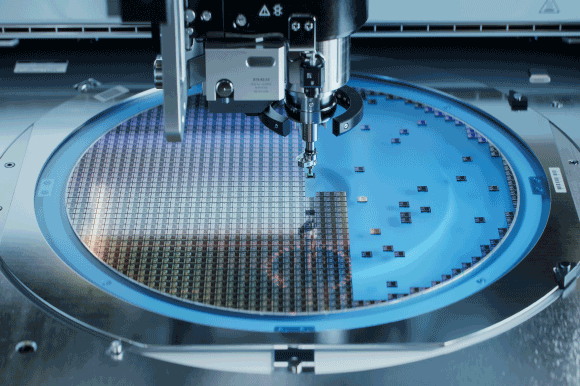

生産現場 計測・検査

【注目】 AI時代の発展を支える半導体製造技術

「シリコンブリッジ技術」とは

先端半導体の技術の中でも微細化と並んで今後の半導体性能を大きく左右する、3次元実装技術。その構成技術のであるシリコンブリッジ技術について解説します。

半導体製造現場の課題を解決!厳選ホワイトペーパー4選(無料)

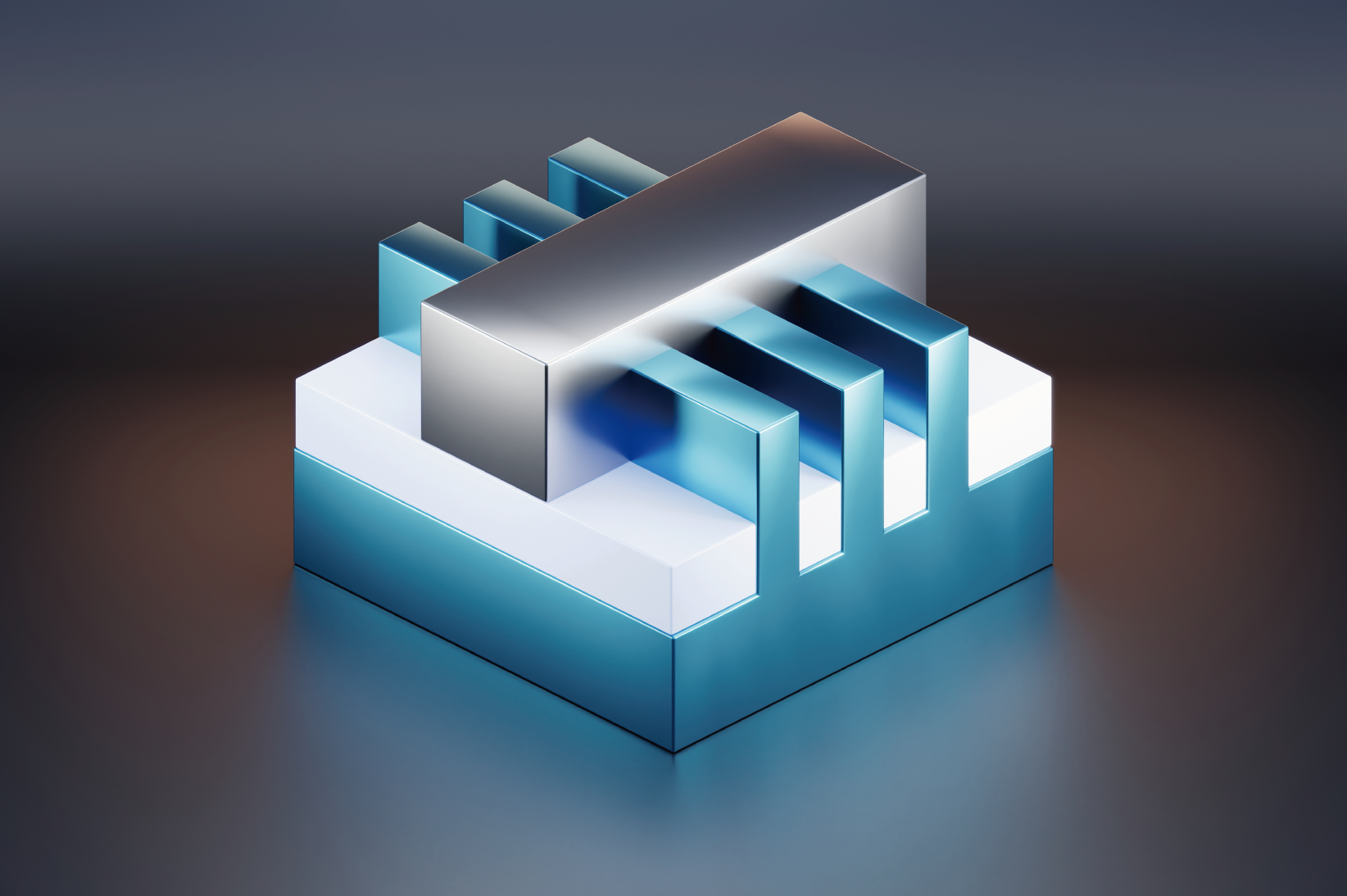

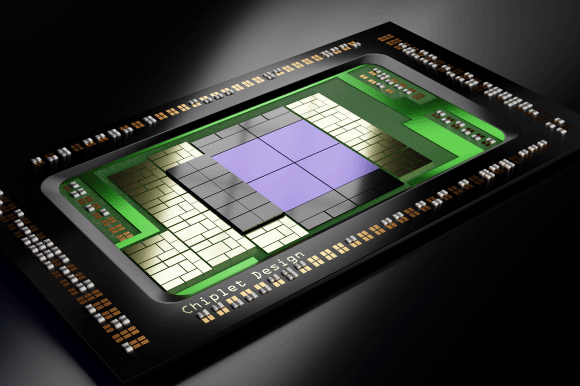

シリコンブリッジ技術とは

シリコンブリッジ技術とは、半導体パッケージ内部に相互接続用のシリコン基板(シリコンブリッジ)を埋め込み半導体パッケージ上部に搭載されるシリコンチップを高密度に実装、相互接続する技術です。

シリコンブリッジの表面に微細かつ高密度な配線を形成することで、隣り合うシリコンチップを近接な距離でパッケージ基板に搭載できるようになります。

シリコンブリッジ技術の特色としては異なるプロセスノードで製造されたチップをパッケージ内で接続することができる点があげられます。これは微細なビア(垂直な電気接続)を使用して、直接的で短い接続を提供することにより、異なるプロセスノードで製造されたチップ間の物理的な間隔を最小限に抑えることができるためです。

また、チップはパッケージ上の任意の位置に配置し、必要に応じてシリコンブリッジを使用して接続することでパッケージ内の空間を最適に利用し、チップ間の距離を最小限に抑えることができます。

これは、ヘテロジニアスパッケージング*¹ として呼ばれ、これにより各チップが最適なプロセスノードで製造することが可能になります。

たとえば、高速演算チップは先端のプロセスノード*² で製造し、同一パッケージに搭載される大容量のメモリチップはより成熟したプロセスノードで製造することが可能です。これにより、全体のパフォーマンスとエネルギー効率を最大化できます。

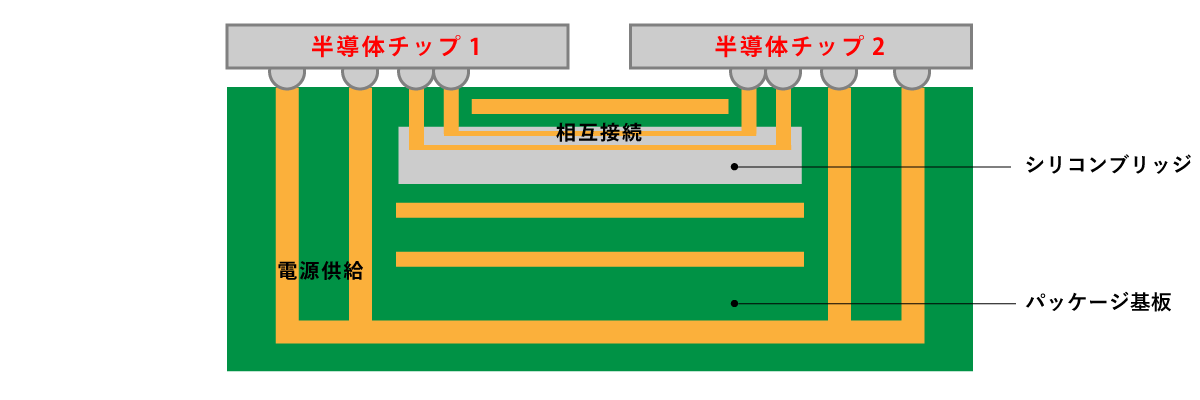

シリコンブリッジ構造詳細

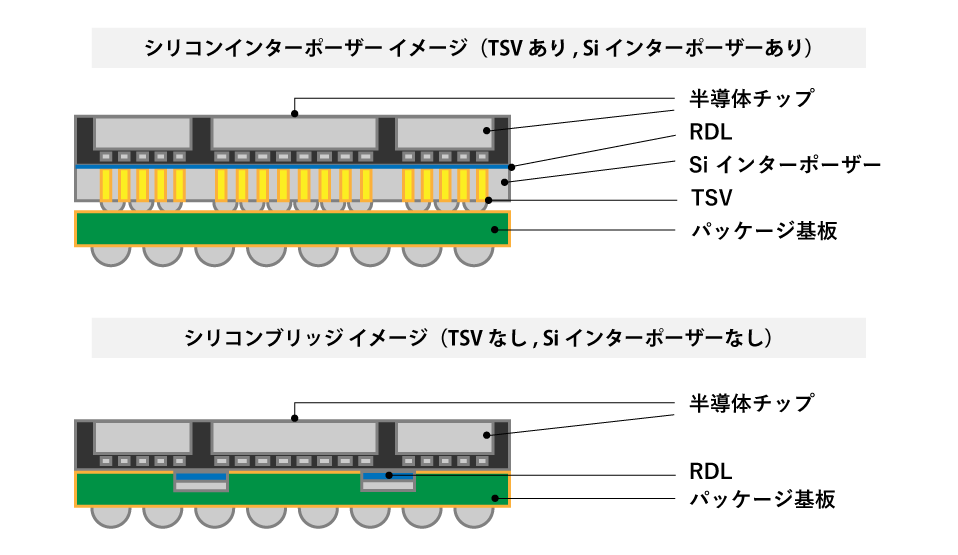

シリコンブリッジ技術とシリコンインターポーザー技術の比較

シリコンインターポーザー技術と比較したときの、シリコンブリッジ技術の利点としては、製造コスト上の利点があります。

シリコンインターポーザ技術に比べると使用するシリコンの面積が小さく済むためコストが少なくて済むほか、シリコンダイの数が増えたときでも、シリコンブリッジの数を増やして対応することで、コストの増加を抑えられます。シリコンインターポーザ技術ではシリコンダイの数が増えると、インターポーザのシリコン面積が巨大になり、コストが増加する傾向にあります。

シリコンブリッジはまた、電源供給をパッケージ基板を通して行うため、シリコンインターポーザー基板で必要となるシリコン貫通ビア(TSV: Through Silicon Via)形成がありません。この点もシリコンインターポーザーと比較した場合のコスト優位点になります。

一方、不利な点としては、シリコンブリッジの接続は、比較的少数のチップ間の接続に限定されることが挙げられます。

理由としては、比較的小さなシリコンブリッジを使用してチップ間を接続するため、シリコンブリッジの数と配置はシリコンブリッジの物理的な大きさと形状に制限されるためです。

大きなパッケージ内で多数のチップを接続するには、シリコンブリッジの数と配置を増やす必要がありますが、これは設計の複雑さと製造コストを増大させるため、シリコンブリッジのコストメリット生かすことができません。

また、大型のシリコンブリッジを介してのチップ間の距離が長くなると、信号伝播の遅延や信号品質の劣化が問題になる可能性があります。これは特に高周波数の信号伝送に影響し、チップ間の通信性能を低下させる可能性があります。

現状では、大量のチップをパッケージ内で高密度に接続するには、シリコンインターポーザーなどの他のパッケージング技術を使用する必要があります。

シリコンブリッジ技術の課題と展望

シリコンブリッジ技術は異なるプロセスノードで製造されたチップをパッケージ内で接続するのに適した技術ですが、広く技術使用されるにあたりいくつかの課題があります。

シリコンブリッジ技術は比較的少数のチップ間の接続に最適化されています。このため、同一パッケージ内で、大量のチップを接続するには、シリコンインターポーザー等、他パッケージング技術などが必要となります。

これは、特にHPCやデータセンターなど、多数のチップを一つのパッケージ内に統合する必要があるアプリケーションにはシリコンブリッジ技術の採用は、現状難しいということを意味しています。

次に、シリコンブリッジはチップ間の高速接続を提供しますが、接続されるチップの物理的な位置と距離に制約があります。チップ間の距離が長くなると、信号伝播の遅延や信号品質の劣化が問題になる可能性があります。これは、高帯域幅と低遅延を要求する高性能アプリケーションに影響を与える可能性があります。

また、シリコンブリッジのプロセスは複雑で、高い精度と製造コントロールを必要とします。これにより、製造コストと信頼性が主要な課題となります。特に、大規模生産においては、製造コストを抑えることと製品の品質と信頼性を確保することの間でバランスを取る必要があります。

今後のシリコンブリッジ技術の展望については、パッケージング技術全体が進化し続けている中で、新しいアプリケーションや要求に対応するために、シリコンブリッジ技術の設計と製造プロセスも進化し続けることが予想されます。これには、より高密度のチップ間接続、より広範なプロセスノード間の互換性、および製造プロセスの改善が含まれます。

例えば、3Dパッケージング技術とシリコンブリッジ技術を組み合わせることで更なるパフォーマンスと機能の向上を図る試みも実施されています。

以上のように、シリコンブリッジ技術は既に半導体技術の一角を占めていますが、今後の技術進歩と市場のニーズによって、先端向けから汎用向けまで、その適用範囲と影響力はさらに拡大すると考えられます。

半導体製造現場の課題を解決!厳選ホワイトペーパー

半導体製造現場の「検査」「監視・調査」「セキュリティ」について、例を挙げて解説しています。日々の業務に是非ご活用ください。

半導体は次の次元へ 微細化から集積へ アドバンストパッケージの世界

【この資料で分かること】

- 市場と技術の未来

- アドバンストパッケージの進化

- ウェーハ加工の課題解決

【こんな方におすすめ】

半導体市場やアドバンストパッケージ技術の動向を把握したい方、製造工程やウェーハ加工における課題解決を求めている方、高速化・高密度化を実現する製造技術に興味がある方、次世代半導体の開発に関わる技術者やエンジニアの方

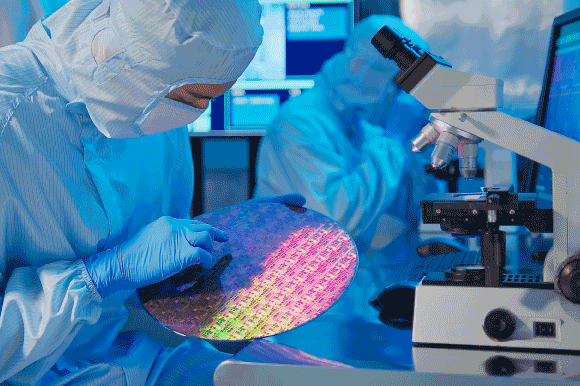

半導体ウェーハの外観検査まるわかりブック

【この資料で分かること】

- 多様なウェーハ材料

- ウェーハ製造工程と外観検査

- 欠陥の種類

- 検査技術のカテゴリ

【こんな方におすすめ】

Siウェーハ、化合物ウェーハ(SiC, GaN, LT/LN, InP), ガラスウェーハ等の検査に関心や課題をお持ちの方

半導体工場の現場DXガイドブック -設備の予知保全、品質監視-

【この資料で分かること】

- 半導体製造工程とDXの取組み

- 製造プロセス監視の作業自動化

- ウェーハ欠陥の原因調査

- 設備稼働監視作業の自動化

- 装置・設備・部品の故障予兆監視

【こんな方におすすめ】

ウェーハ製造工場や、デバイス製造工場のファシリティ設備の業務課題に関心や課題をお持ちの方

OTを止めるな!!半導体業界に必須のサイバー攻撃対策

【この資料で分かること】

- 外部脅威を排除しセキュアな工場へ

- 内部関係者によるリスク対策

- サプライチェーンリスク

- 横感染

- リスク発生&対策ソリューションマップ

【こんな方におすすめ】

半導体製造工場の現場、IT担当者、半導体装置メーカーでセキュリティに関心と課題をお持ちの方

用語集

*¹ ヘテロジニアスパッケージング:ヘテロジニアスパッケージングとは、異なるタイプや機能を持つ半導体チップを一つのパッケージ内に集約するパッケージング技術のことを指します。この技術は、各チップが最適なプロセスノードで製造されることを可能にし、さまざまな機能を一つのパッケージに統合することができます。

*² プロセスノード:プロセスノードとは、半導体製造技術の精密さを示す指標の一つで、主にトランジスタのサイズや密度を表すために使用されます。プロセスノードの数値は小さいほど、同じ面積内により多くのトランジスタを配置できることを示し、一般的には性能が高く、エネルギー効率が良いとされています。具体的な数値としては、90nm、65nm、45nm、32nm、22nm、14nm、10nm、7nm、5nm、3nmなどがあります。