- HOME

- 【注目】AI時代の発展を支える半導体製造技術 「先端パッケージ実装」とは

生産現場 計測・検査

【注目】AI時代の発展を支える半導体製造技術

「先端パッケージ実装」とは

半導体パッケージ基板とは

半導体パッケージ基板とは、半導体チップと配線板(PCB)との間で電気信号を伝達するために使用されます。

半導体パッケージ基板としては、主にリードフレーム型と積層基板型が使用されています。リードフレーム型はワイヤーボンド*²でリードフレームと接続し、リードフレームを通してメイン基板と接続します。パワーデバイス等に使用されています。

積層基板型はチップ側に半田バンプを形成し、それを半導体基板側回路に接続しています。(フリップチップ実装)

半導体基板側と配線板とはBGA(ボールグリッドアレイ)*³で接続されます。リードフレーム型に比べて小型化、多ピン化が可能なためSoC等のシステムLSIの実装用途で使用されています。

積層基板型のパッケージ基板は配線板とくらべ、チップ実装のための高密度化が図られており、回路形成もセミアディティブプロセス(SAP)*¹というメッキ法で微細化が進んでいます。

ワイヤーボンド実装実装のイメージ図 (側面側)

![]()

FC(フリップチップ)実装のイメージ図 (側面側)

![]()

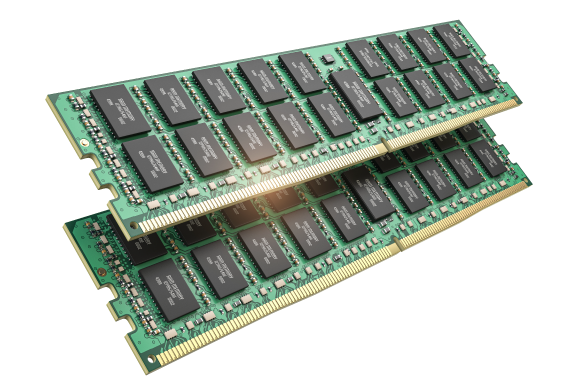

現在主流の先端パッケージについて

近年スマホやHPCに使用される先端半導体チップでは、高速度化、低消費電力化、小型・薄型化の要求が高まってきております。そのため、先端半導体パッケージ基板側にも同様に3つのポイントが求められています。

1.高密度実装による小型化

2.多機能化による高ピン化

3.高性能化に対応した高放熱性・高電気特性

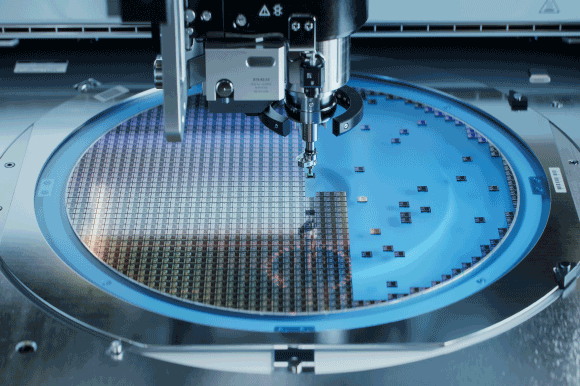

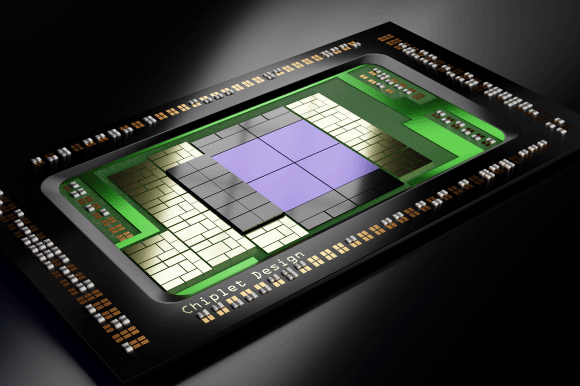

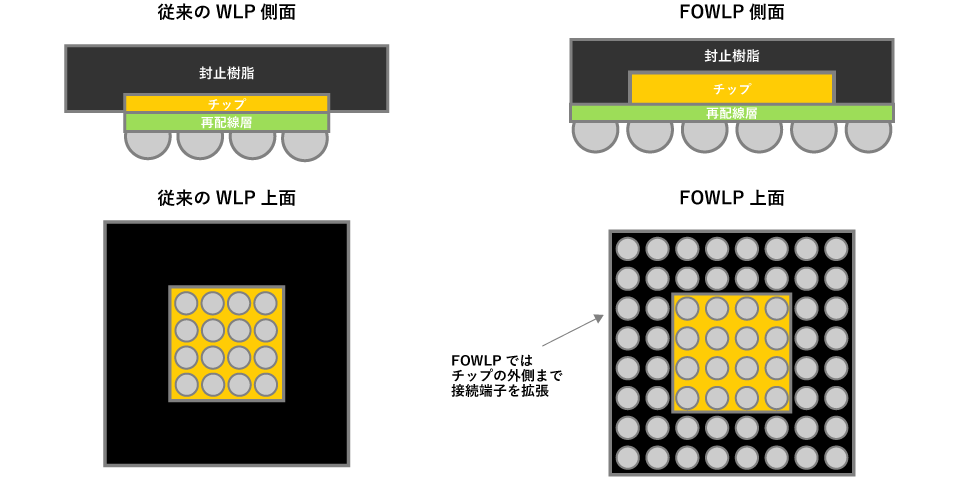

これらの技術要求にこたえるために半導体パッケージにおいても新しいパッケージ技術が導入されてきています。その代表的にな技術がFOWLP(Fan Out Wafer Leve Package)です。

この技術はウェーハ上でパッケージを完成させるWLCSP(Wafer Level Chip Scale Package)*⁴ 技術をベースに、前工程の製造技術を使用して生成する再配線層をチップ上だけでなくパッケージエリアまで広げることにより接続端子数を増やし、高ピン化に対応しています。

配線板と接続する半田バンプは再配線層に直接形成されるので、フリップチップ実装で必要される、半導体パッケージ基板が不要となり、フリップチップ実装よりさらにパッケージ全体の低背化が可能となりました。

FC(フリップチップ)実装とFOWLP実装とのパッケージ高さイメージ図

![]()

従来のWLPとFan out WLP の端子位置比較イメージ図

FOWLPの課題

FOWLPの課題としては、現在はその薄化特性を生かしたモバイル向けの用途が主となりますが、今後需要が拡大する高集積化要求のあるHPCやAI向けのパッケージとして、マルチチップ化やチップレットへの対応があげられます。

近年は、高集積化のために、インターポーザー基板にFOWLPのチップを搭載するなどの新しい技術も登場してきています。また環境変化の激しい車載向けに搭載するために、放熱性や耐久性を高める必要があります。

FOWLP技術は、既存パッケージング技術やインターポーザー技術と組み合わせることで幅広い用途で使用されることを想定し、現在の半導体パッケージ技術の進化を牽引しています。

半導体製造現場の課題を解決!厳選ホワイトペーパー

半導体製造現場の「検査」「監視・調査」「セキュリティ」について、例を挙げて解説しています。日々の業務に是非ご活用ください。

半導体は次の次元へ 微細化から集積へ アドバンストパッケージの世界

【この資料で分かること】

- 市場と技術の未来

- アドバンストパッケージの進化

- ウェーハ加工の課題解決

【こんな方におすすめ】

半導体市場やアドバンストパッケージ技術の動向を把握したい方、製造工程やウェーハ加工における課題解決を求めている方、高速化・高密度化を実現する製造技術に興味がある方、次世代半導体の開発に関わる技術者やエンジニアの方

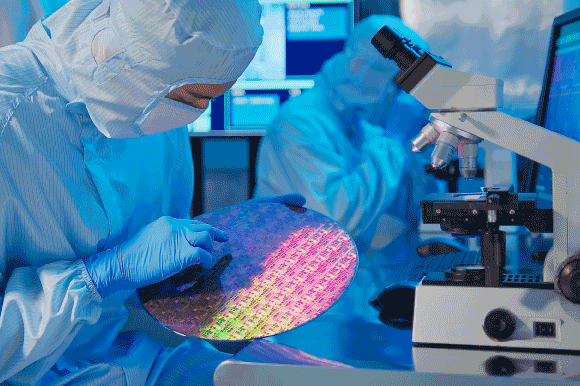

半導体ウェーハの外観検査まるわかりブック

【この資料で分かること】

- 多様なウェーハ材料

- ウェーハ製造工程と外観検査

- 欠陥の種類

- 検査技術のカテゴリ

【こんな方におすすめ】

Siウェーハ、化合物ウェーハ(SiC, GaN, LT/LN, InP), ガラスウェーハ等の検査に関心や課題をお持ちの方

半導体工場の現場DXガイドブック -設備の予知保全、品質監視-

【この資料で分かること】

- 半導体製造工程とDXの取組み

- 製造プロセス監視の作業自動化

- ウェーハ欠陥の原因調査

- 設備稼働監視作業の自動化

- 装置・設備・部品の故障予兆監視

【こんな方におすすめ】

ウェーハ製造工場や、デバイス製造工場のファシリティ設備の業務課題に関心や課題をお持ちの方

OTを止めるな!!半導体業界に必須のサイバー攻撃対策

【この資料で分かること】

- 外部脅威を排除しセキュアな工場へ

- 内部関係者によるリスク対策

- サプライチェーンリスク

- 横感染

- リスク発生&対策ソリューションマップ

【こんな方におすすめ】

半導体製造工場の現場、IT担当者、半導体装置メーカーでセキュリティに関心と課題をお持ちの方

用語集

*¹ セミアディティブプロセス(SAP):セミアディティブプロセスとは配線板表面に配線形成するためにフォトレジストを使用する方法です。半導体チップを接続するためのボンディングパッドや配線のパターンを形成するために、UVライトを使用して露光することができます。

*² ワイヤーボンド:ワイヤーボンドとは、半導体チップとリードフレームを電気的に接合するために、ワイヤーを用いて接続する手法です。ワイヤーには金、アルミニウム、銅等が使用されます。

*³ BGA(ボールグリッドアレイ):BGAは、集積回路に使用される表面実装パッケージの一種です。パッケージ背面に形成した半田ボールでチップと配線板を接続します。

*⁴ WLCSP(Wafer Level Chip Scale Package):WLCSPとはウェーハ基板上で半導体パッケージを完成させるパッケージ手法です。パッケージ基板に搭載せずにパッケージを完成させるので、パッケージをチップサイズに合わせて最小化することができます。