- HOME

- 【注目】 AI時代の発展を支える半導体製造技術 「ガラスコア基板」とは

生産現場 計測・検査

【注目】 AI時代の発展を支える半導体製造技術

「ガラスコア基板」とは

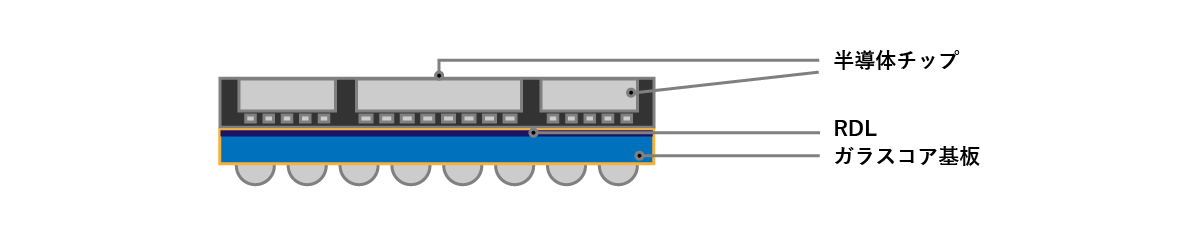

先端半導体の技術の中でも微細化と並んで今後の半導体性能を大きく左右する、3次元実装技術。その構成技術であるガラスコア基板 について解説します。

半導体製造現場の課題を解決!厳選ホワイトペーパー4選(無料)

ガラスコア基板とは

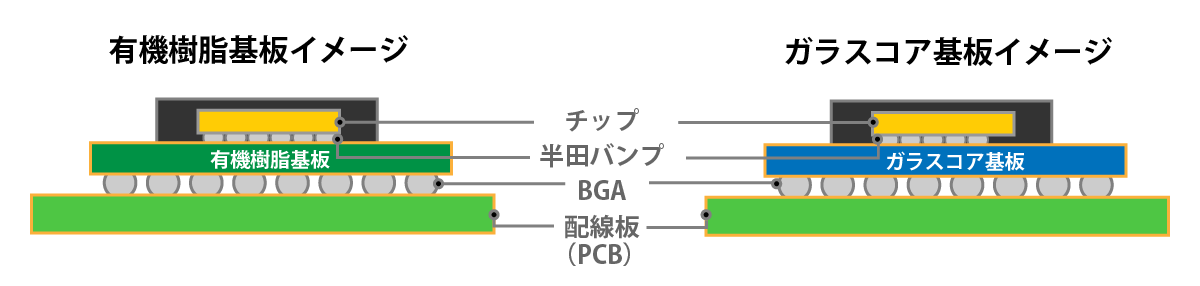

ガラスコア基板とは、半導体チップをPCB基板と接続するためのICサブストレート*¹ の1種です。ICサブストレートはそれを構成するコア基板の材料によっていくつか種類があります。

現在の高密度実装において使用されているのは、有機樹脂コア基板を使用したICサブストレートですが、ガラスをコア基板とした新しいICサブストレートを2020年代後半の量産をめざして、現在進行形で開発が進んでいます。

ガラスコア基板は、有機樹脂基板に比べて多くの利点を持っています。

高い絶縁性と高速通信への適応

絶縁性が高く、クロストーク*² や電磁ノイズの影響が少ないため、高速通信や高周波信号の伝送に適しています。次に、熱膨張係数がシリコンと近いため、温度変化による歪みが抑えられ、チップとの接続が安定します。

寸法安定性と高密度実装への適応

寸法安定性に優れ、温度や湿度の影響を受けにくいため、微細配線や高密度実装に最適です。高周波信号の損失が少ないことから、5Gや6G通信、RFデバイスにも対応可能です。

高い熱伝導性と耐環境性による信頼性

ガラスは熱伝導性が高いため、発熱量の多いデバイスに適しており、有機樹脂基板よりも効率的に放熱できます。耐環境性も高く、厳しい条件下でも長期間安定した性能を発揮するため、信頼性が求められる分野での利用が期待されます。

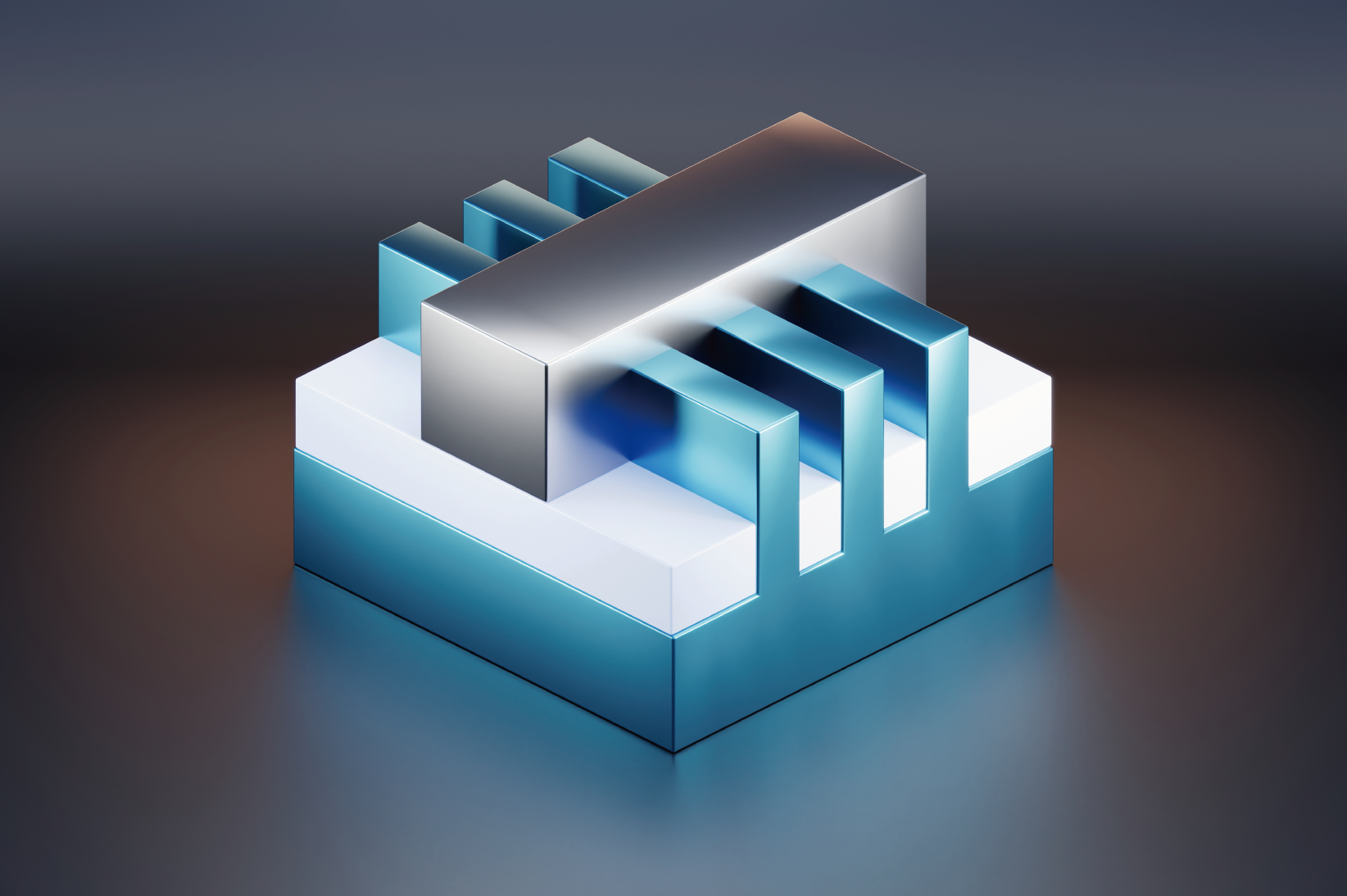

有機樹脂基板とガラスコア基板の比較図

ガラスコア基板開発の背景

ガラスコア基板開発の背景としては、AI半導体向けICサブストレートの大型化需要があります。

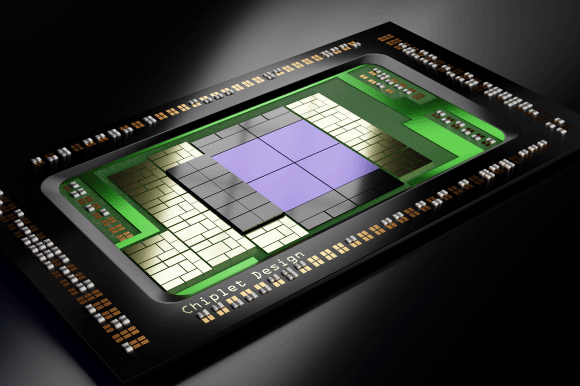

AI向けの高機能半導体では、チップを機能ごとに分割するチップレット構造の採用が進み、さらに性能アップのためにチップレットを構成するダイの大型化とダイ数の増加が見込まれます。

そのためチップレット搭載する、インターポーザー基板のサイズも拡大し、インターポーザー基板が搭載されるICサブストレートのサイズも大型化が必要となります。

具体的には、サーバーやデータセンター向けのFC-BGA(フリップチップボールグリッドアレイ)*³ のICサブストレートサイズは、2022年の56mm×100mmから、2026年には120mm×120mmへと拡大し、将来的にはさらなる大型化が予想されます。

従来の有機樹脂ICサブストレート

従来の有機樹脂ICサブストレートでは、大型化に伴う寸法安定性、熱膨張係数、剛性、放熱性能といった問題があり、次世代の高性能・高密度アプリケーションへの対応が難しいとされています。

これに対し、ガラスコア基板は、これらの課題を克服するための有望な技術として注目されており、HPCやデータセンター向けの大型サブストレートには、ガラス基板が採用される傾向が強まっています。

ガラスコア基板を使うメリット

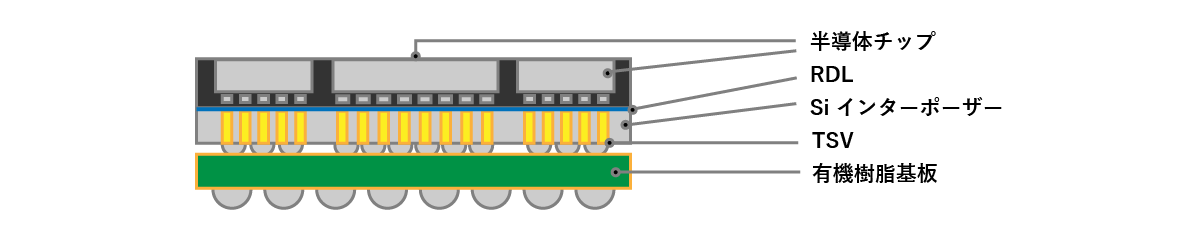

将来的なガラスコア基板を使うメリットとしては、有機樹脂基板に比べて平滑な面を形成することが可能なため、半導体前工程プロセスを使用した微細加工で、ガラスコア基板上に直接微細RDL層を形成し、Siインターポーザーレスの構造をとることも技術的には可能となります。

Siインターポーザーは大型化するとダイ間信号の減衰がおき、性能低下につながるため、ガラスコア基板の高速通信に適した材料特性が次世代コンピューティングの進化に寄与することが期待されています。

またAI半導体の電力消費を劇的に減らすことができる技術として期待を集める光電融合技術においても、電気と光の信号を変換する光トランシーバーをガラスコア基板実装する際に、従来の有機樹脂基板と比較して信頼性と効率性が向上し、AI使用時に発生する莫大な消費電力低減への寄与が期待されます。

Siインターポーザーとガラスコア基板を使用した集積比較図

シリコンインターポーザー 実装イメージ

ガラスコア基板実装 イメージ(Siインターポーザーなし)

ガラスコア基板の課題と展望

ガラスコア基板は、半導体パッケージング技術において高い可能性を秘めておりますが、いくつかの技術的課題に直面しております。

ガラスコア基板の課題

微細配線技術の限界

まず、第一に挙げられる課題は、微細配線技術の限界です。現在のガラスコア基板では、最小L/S(ライン/スペース)が2μm程度であり、Siインターポーザーの1μm未満の技術に比べて劣っています。

このため、ガラスコア基板を高密度な集積回路に適用するには、さらなる微細化技術の開発が必要です。

微細化が進まない限り、高性能なデバイス間でのデータ伝送速度や処理効率は、Siインターポーザーを上回ることが難しい状況です。

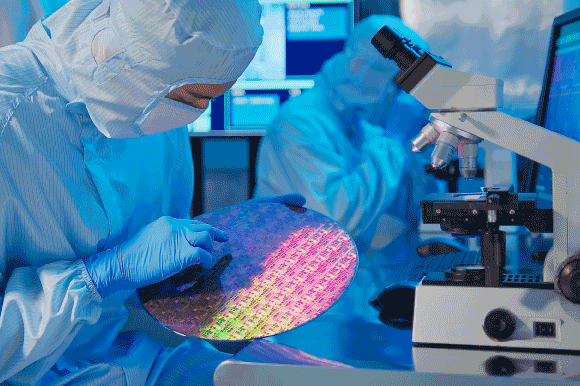

TGV技術の成熟度と生産効率の課題

次に、TGV(Through Glass Via)*³ 技術の成熟度が課題となっています。ガラスコア基板では、ガラス素材に貫通ビア(TGV)を形成して信号を伝送しますが、現時点ではこの技術のコストが高く、製造工程の複雑さが問題となっております。

TGVの形成にはレーザーや化学エッチングが使用されますが、これらのプロセスがガラスに与える影響を最小限に抑える必要があります。

特に、加工中にクラックや損傷が発生しやすいため、生産の歩留まり向上が大きな課題です。

また、TGVのピッチ(ビア間隔)がSiインターポーザーに比べて大きく、配線密度が制約されている点も、今後解決すべき課題です。

製造コストの高さと量産プロセスの課題

製造コストの高さも課題の一つです。ガラスコア基板は材料自体のコストは比較的低いものの、微細加工やTGVの形成プロセスに多くのコストがかかります。このため、大規模生産を目指すアプリケーションでは、コスト面での競争力が低下する恐れがあります。

特に、Siインターポーザーが広く採用されている分野では、ガラスコア基板の導入が進みにくい要因となる可能性があります。そのため、製造プロセスの効率化やコスト削減が今後の技術開発の重要な課題となるでしょう。

ガラスコア基板の展望

高い絶縁性と高周波信号伝送への適応

一方、ガラスコア基板の利点として、ガラスの物理的特性が優れていることが挙げられます。ガラスは高い絶縁性を持ち、電気的損失が少ないため、高周波数帯での信号伝送に適しています。

これにより、次世代通信技術(5G/6G)や高性能コンピューティング(HPC)など、データの高速処理を求める分野での活躍が期待されます。

熱膨張係数の一致による信頼性の高いパッケージング

また、ガラスの熱膨張係数がシリコンと近いため、温度変化に伴う反りやひずみが少なく、信頼性の高いパッケージングが可能です。

コスト効率と大規模製造への貢献

さらに、ガラスコア基板はコスト効率の向上にも寄与する可能性があります。Siインターポーザーに比べ、ガラスコア基板は大型パネルでの製造が可能であり、これにより一度に多くのチップを実装できる点が、大規模な製造プロセスにおいてコスト削減に貢献します。

このため、消費者向けの電子機器やIoTデバイスなど、量産が求められる分野での採用が進むことが期待されます。また、材料の入手しやすさと加工技術の進展に伴い、製造コストの削減が進む可能性も高いです。

Siブリッジとの統合による高性能化

最後に、今後の技術開発においては、Siブリッジとの統合技術が重要な展望となっています。ガラスコア基板にSiブリッジを内蔵することで、複数のチップ間の高速な信号伝送が可能になり、高密度かつ高性能なシステムインパッケージ(SiP)の構築が期待されます。

Siブリッジとガラスコア基板の組み合わせにより、Siインターポーザーに匹敵する性能を発揮しながら、コスト効率の向上が見込まれています。

このようなハイブリッド技術は、次世代半導体パッケージングの主流になる可能性があります。

以上ガラスコア基板は、微細化やTGV技術、製造コストといった課題に直面しておりますが、その優れた物理特性やコスト効率の高さから、今後幅広い分野での採用が進むことが期待されます。

技術革新が進み、これらの課題が解決されれば、ガラスコア基板は次世代半導体パッケージング技術の中核として、Siインターポーザーに代わる存在になる可能性を期待されています。

半導体製造現場の課題を解決!厳選ホワイトペーパー

半導体製造現場の「検査」「監視・調査」「セキュリティ」について、例を挙げて解説しています。日々の業務に是非ご活用ください。

半導体は次の次元へ 微細化から集積へ アドバンストパッケージの世界

【この資料で分かること】

- 市場と技術の未来

- アドバンストパッケージの進化

- ウェーハ加工の課題解決

【こんな方におすすめ】

半導体市場やアドバンストパッケージ技術の動向を把握したい方、製造工程やウェーハ加工における課題解決を求めている方、高速化・高密度化を実現する製造技術に興味がある方、次世代半導体の開発に関わる技術者やエンジニアの方

半導体ウェーハの外観検査まるわかりブック

【この資料で分かること】

- 多様なウェーハ材料

- ウェーハ製造工程と外観検査

- 欠陥の種類

- 検査技術のカテゴリ

【こんな方におすすめ】

Siウェーハ、化合物ウェーハ(SiC, GaN, LT/LN, InP), ガラスウェーハ等の検査に関心や課題をお持ちの方

半導体工場の現場DXガイドブック -設備の予知保全、品質監視-

【この資料で分かること】

- 半導体製造工程とDXの取組み

- 製造プロセス監視の作業自動化

- ウェーハ欠陥の原因調査

- 設備稼働監視作業の自動化

- 装置・設備・部品の故障予兆監視

【こんな方におすすめ】

ウェーハ製造工場や、デバイス製造工場のファシリティ設備の業務課題に関心や課題をお持ちの方

OTを止めるな!!半導体業界に必須のサイバー攻撃対策

【この資料で分かること】

- 外部脅威を排除しセキュアな工場へ

- 内部関係者によるリスク対策

- サプライチェーンリスク

- 横感染

- リスク発生&対策ソリューションマップ

【こんな方におすすめ】

半導体製造工場の現場、IT担当者、半導体装置メーカーでセキュリティに関心と課題をお持ちの方

用語集

- *¹ ICサブストレート

- ICサブストレートは、半導体チップとPCB基板を接続するための中間層で、電気的信号の伝達や電源供給をサポートし、チップの機械的な強度を提供します。

- *² クロストーク

- クロストークとは、隣接する信号回路や通信路間での電気的な干渉を指します。この干渉により、信号の品質が低下し、誤動作やノイズの発生が起こることがあります。

- *³ FC-BGA(フリップチップボールグリッドアレイ)

- FC-BGA(Flip Chip Ball Grid Array)は、ICパッケージ技術の一種で、チップを反転させて基板に接続します。高密度実装が可能で、主に高性能なプロセッサやGPUに使用され、熱管理や電気的特性に優れています。

- *⁴ TGV(Through Glass Via)

- TGV(Through Glass Via)は、ガラス基板に垂直に穴を開け、配線を通す技術です。ガラス基板を用いることで、優れた熱特性や高周波特性を持ち、半導体パッケージングや高密度実装に利用されています。