- HOME

- 【注目】AI時代の発展を支える半導体製造技術 「3次元集積技術」とは

生産現場 計測・検査

【注目】AI時代の発展を支える半導体製造技術

「3次元集積技術」とは

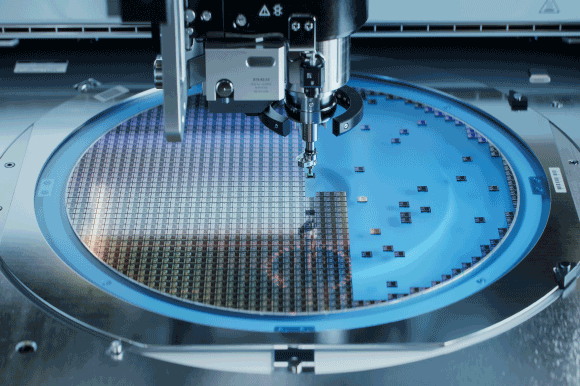

先日日本でも量産化に向けて動き出したことが話題になっている先端半導体。その先端半導体の技術の中でも微細化と並んで今後の半導体性能を大きく左右する、3次元実装技術について解説します。

半導体3次元集積化の背景

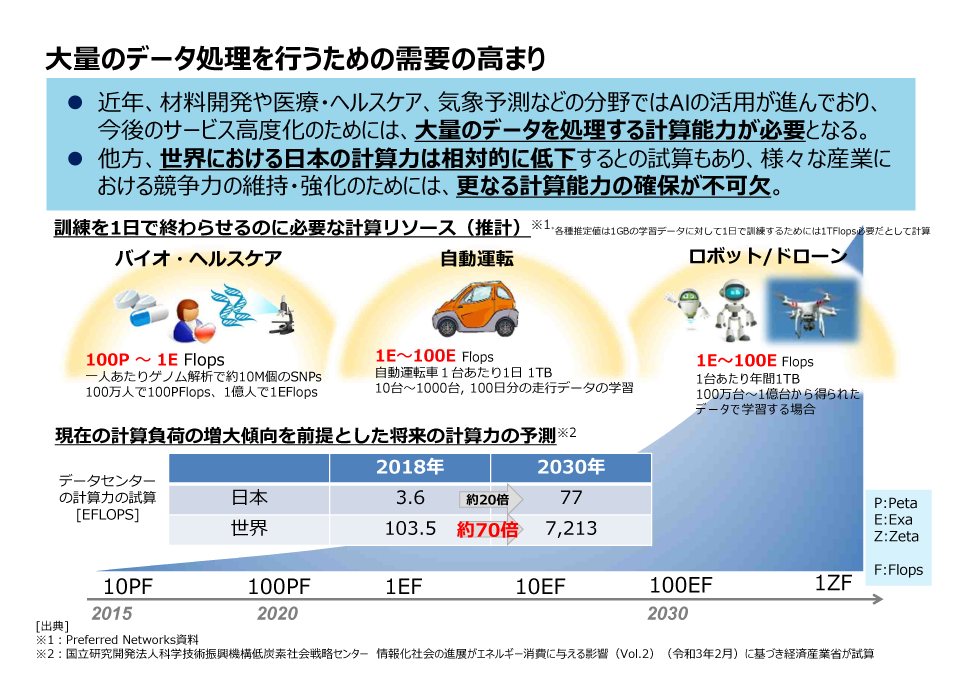

半導体3次元集積化の背景として、近い将来に社会実装が期待されるAI、自動運転、メタバース等は現在と比較し、莫大なデータ処理が必要となり、演算処理能力の大幅な性能アップが必要となります。

しかし、実際には先端半導体の微細化速度のスローダウンと、物理的な微細化の限界が近づいており、既存の技術だけでは将来的な演算要求性能を達成するのが難しくなることが予想されています。

また環境の問題としては先端半導体の製造コストは、世代を追うごとに上昇し、かつ製造に使用される消費電力も増大しており、サステナブル社会を実現するうえでの課題となっています。

そのため、コスト低減に有効で、低消費電力につながり、またデバイス全体の性能をあげることができる3次元実装技術に注目が集まっています。

将来的なデータ処理需要の高まりイメージ

経済産業省 第5回 半導体・デジタル産業戦略検討会議

~デジタル産業基盤のサプライチェーン強靱化に向けて~ 2022年より抜粋

https://www.meti.go.jp/policy/mono_info_service/joho/conference/semicon_digital/0005/03.pdf

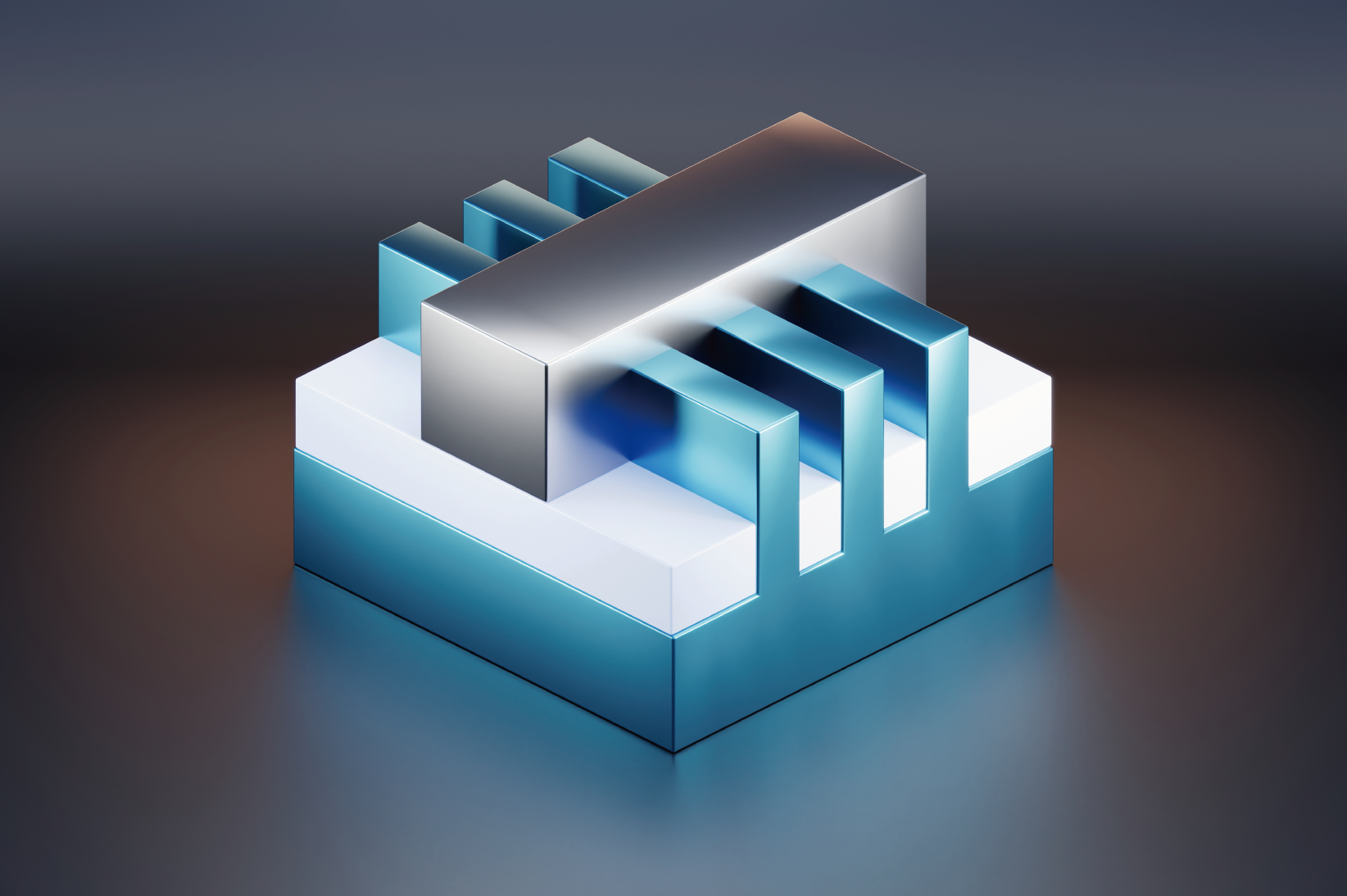

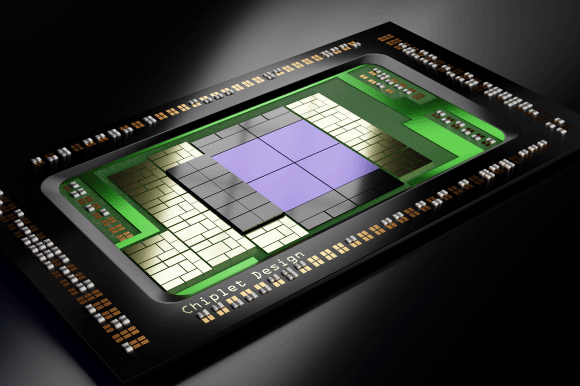

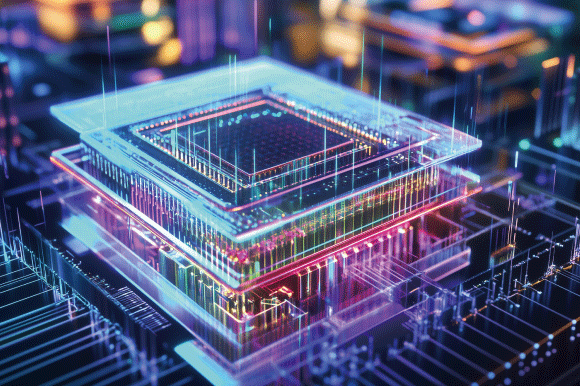

半導体3次元集積化の構成技術

3次元集積の構成技術については、主に以下の2種類があります。

- 半導体チップ自体を垂直方向に積層し、相互接続することにより高集積化を図る技術

- チップを同一面内に並べて、インターポーザー*¹等を介して相互接続し、処理の最適化をおこなう技術

この2つの集積化技術を組み合わせて使用することにより全体の処理能力向上と消費電力の低減の両立をめざしています。これらの技術詳細については、次回以降に詳しく説明します。

半導体チップ3次元集積のイメージ図(側面側)

![]()

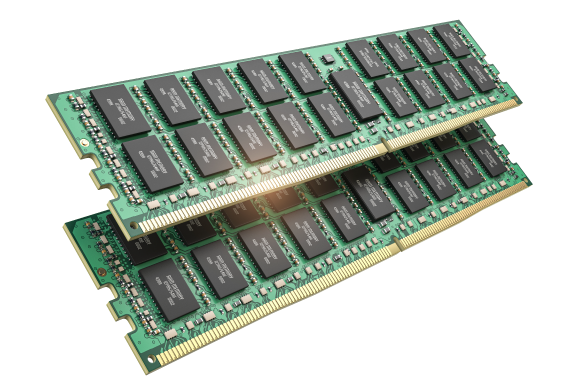

3次元集積半導体今後の展望

3次元集積を含む先端半導体は現在主にスマートフォンで使用されていますが、既にスマートフォンの高性能化は飽和しつつあり、先端半導体はスマートフォンにとって過剰スペックになりつつあります。その代わりに近年はサーバー等に使用される、HPC*²(High performance computing)が先端半導体の主用途になりつつあり、今後もこの傾向は続いていくと思われます。

さらに今後IoT社会であらゆるものがインターネットで接続され、高速通信でリアルタイムにデータ通信が可能になると、データ通信量は増大し、さらなる高速演算処理が必要となります。

そのため現在のようにデータをクラウドサーバにおくり、そこで演算処理をするのは効率が悪いため、一度ローカルネットワークで情報処理し、その中で必要なデータだけをクラウドサーバーにて演算処理する必要がでてきます。

このようなローカルでの情報演算処理のための、エッジコンピューティング*³とAIの用途としても将来的には先端半導体が使用されます。

半導体の性能UPを享受するのが、ヒトからモノに代わっていく中で、社会インフラとしての先端半導体の重要性は今後ますます高まっていくと考えられています。

2040年の社会予想図

経済産業省 未来イノベーションWG 第1回事務局資料 2019年より抜粋https://www.meti.go.jp/shingikai/mono_info_service/mirai_innovation/pdf/001_04_00.pdf

半導体製造現場の課題を解決!厳選ホワイトペーパー

半導体製造現場の「検査」「監視・調査」「セキュリティ」について、例を挙げて解説しています。日々の業務に是非ご活用ください。

半導体は次の次元へ 微細化から集積へ アドバンストパッケージの世界

【この資料で分かること】

- 市場と技術の未来

- アドバンストパッケージの進化

- ウェーハ加工の課題解決

【こんな方におすすめ】

半導体市場やアドバンストパッケージ技術の動向を把握したい方、製造工程やウェーハ加工における課題解決を求めている方、高速化・高密度化を実現する製造技術に興味がある方、次世代半導体の開発に関わる技術者やエンジニアの方

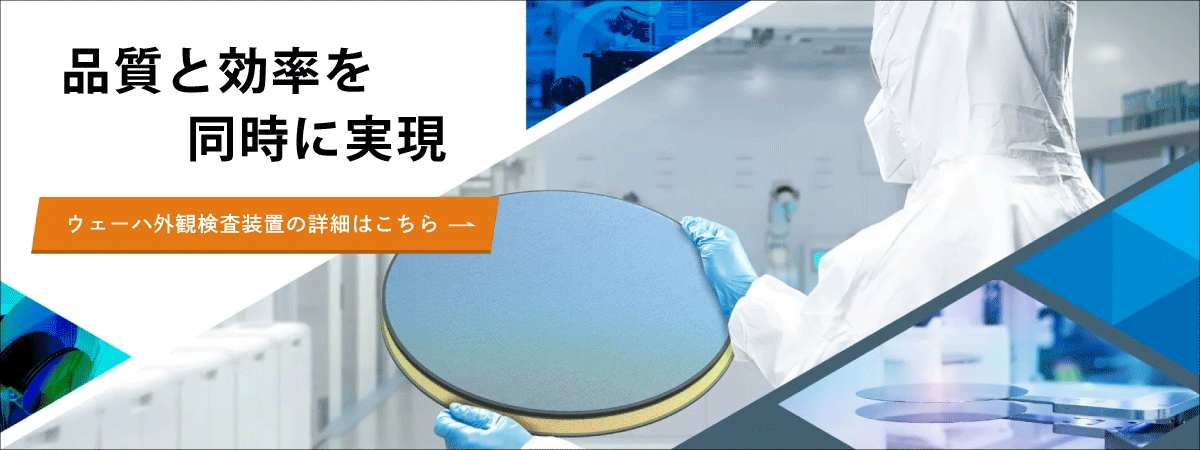

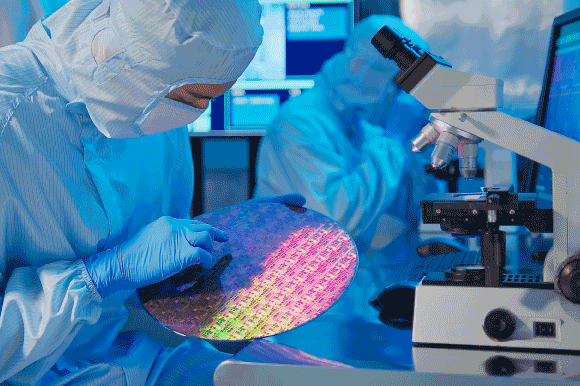

半導体ウェーハの外観検査まるわかりブック

【この資料で分かること】

- 多様なウェーハ材料

- ウェーハ製造工程と外観検査

- 欠陥の種類

- 検査技術のカテゴリ

【こんな方におすすめ】

Siウェーハ、化合物ウェーハ(SiC, GaN, LT/LN, InP), ガラスウェーハ等の検査に関心や課題をお持ちの方

半導体工場の現場DXガイドブック -設備の予知保全、品質監視-

【この資料で分かること】

- 半導体製造工程とDXの取組み

- 製造プロセス監視の作業自動化

- ウェーハ欠陥の原因調査

- 設備稼働監視作業の自動化

- 装置・設備・部品の故障予兆監視

【こんな方におすすめ】

ウェーハ製造工場や、デバイス製造工場のファシリティ設備の業務課題に関心や課題をお持ちの方

OTを止めるな!!半導体業界に必須のサイバー攻撃対策

【この資料で分かること】

- 外部脅威を排除しセキュアな工場へ

- 内部関係者によるリスク対策

- サプライチェーンリスク

- 横感染

- リスク発生&対策ソリューションマップ

【こんな方におすすめ】

半導体製造工場の現場、IT担当者、半導体装置メーカーでセキュリティに関心と課題をお持ちの方

用語集

- *¹ インターポーザー

- パッケージ基板(樹脂基板)とシリコンダイに間にある中間基板のことでシリコンダイをインターポーザーを層を使い電気的に接続します。パッケージ基板(樹脂基板)の上にシリコンの中間基板(インターポーザ)を置き、その上に複数のシリコンダイを横に近接して並べます。シリコンインターポーザの表面(上側)には、多層配線の回路を形成してあり、TSVによって裏面(下側)の樹脂基板と接続します。

- *² HPC

- ハイパフォーマンス・コンピューティングの略で、膨大なデータに対し複雑な演算処理を高速に実行するシステムの総称です。スーパーコンピュータ、量子コンピュータもHPC領域に含めることができます。チップの構成としては、CPU、GPU、FPGA等に大別されます。

- *³ エッジコンピューティング

- TSV(Through-Silicon-Via)はシリコンウェーハを貫通する垂直配線のことです。