- HOME

- 【注目】 AI時代の発展を支える半導体製造技術 「CFET」とは

生産現場 計測・検査

【注目】 AI時代の発展を支える半導体製造技術

「CFET」とは

先端半導体の技術の中でも微細化と並んで今後の半導体性能を大きく左右する、3次元実装技術。その構成技術であるCFETについて解説します。

半導体製造現場の課題を解決!厳選ホワイトペーパー4選(無料)

CFETとは

CFETとは、Complementary Field-Effect Transistorの略で、2030年以降1nm以下のプロセスノードで採用が検討されているトランジスターの製造方法です。

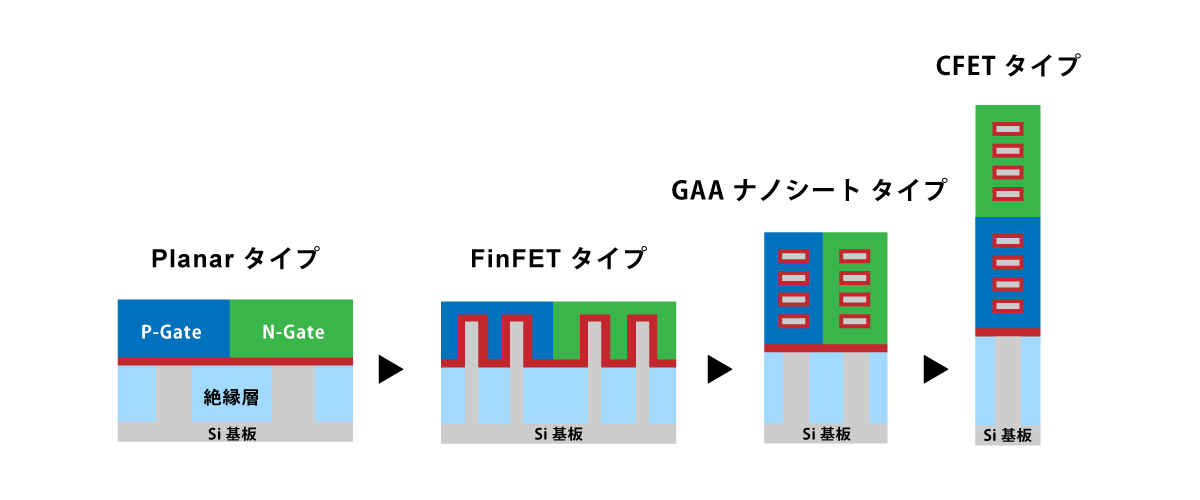

2025年量産を目標に開発が進んでいる最先端の2nmプロセスで使用されるGAA(Gate all around)*¹ 方式のトランジスターは、CMOSトランジスターのスタンダードセルを構成するPMOS/NMOS*² が横並びにならんでいますが、CFETではPMOS/NMOSを垂直方向にスタックして配置します。

そのため、CFETはサイズが小さく、効率が高いという特徴があります。さらに、CFETは低電力で動作するため、省エネルギーの面で有利です。特に、スマートフォンやコンピューターなどの電子機器において、より高速で省電力な半導体デバイスが求められているアプリケーションに対して、CFETは重要な技術となることが予想されています。

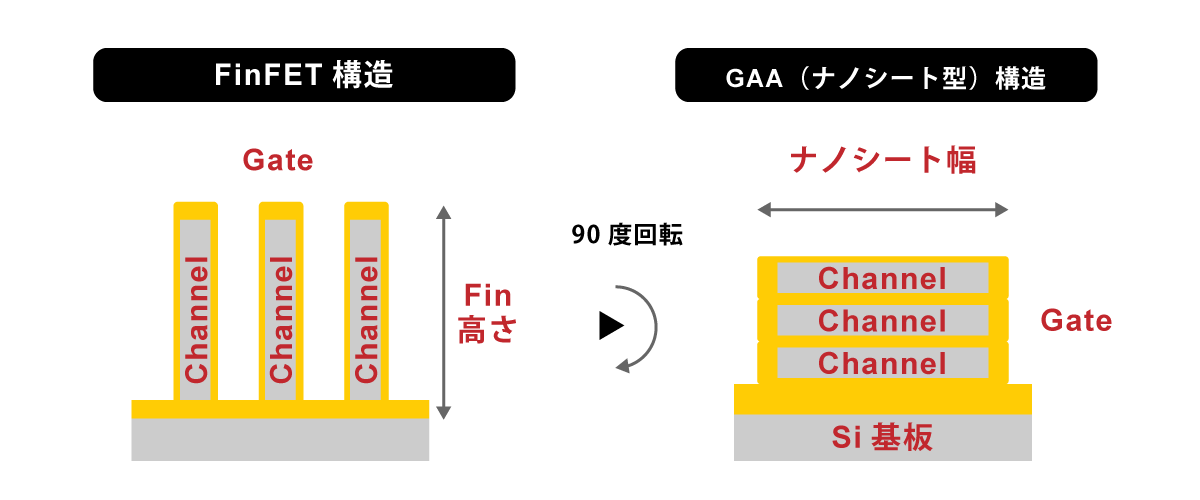

FinFETとGAAの構造比較(断面図)

CFET採用の背景

CFET採用の背景としては、デバイス性能を向上させるためにゲートピッチを縮小する従来の微細化が物理的な限界に近づいてきており、トランジスタを構成するセルサイズ全体を縮小することでデバイス性能を向上させる必要がでてきているためです。その流れの中で従来のPlanar型からFinFET、GAA、CFETとトランジスタ構造を変えてデバイスの進化を進める試みが続いています。

セルサイズを縮小するためには、ゲート幅の縮小、トランジスタ密度の向上とともに、ゲートに対して、垂直に設置されるメタルトラックを減少し、セルハイトを減少させる必要があります。

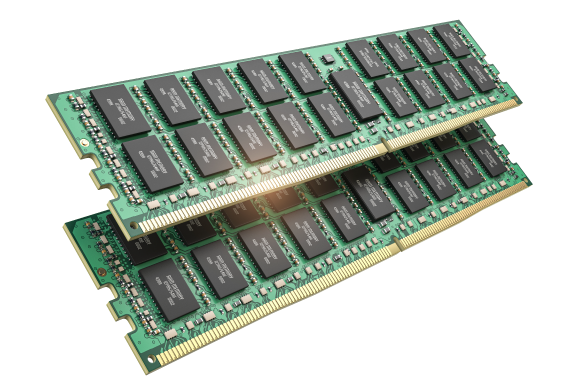

通常のPlanar型で10トラック以上あったメタルトラックをFinFET,GAAとも5トラックまで、減少させることができましたが、さらなる低背化のためにセルを1つ失くすに等しいCFETの採用が検討されています。

またPMOSとNMOSを垂直に重ねることにより、PN距離*³ が短くなり、動作速度の向上、省エネルギー効果が期待できます。

トランジスタ構造進化の歴史(断面図)

CFETの製造方法

CFET(Complementary Field-Effect Transistor)の製造方法には、主に「モノリシック(Monolithic)」と「シークエンシャル(Sequential)」という二つのアプローチがあります。これらの方法は、n型とp型のトランジスタをどのように統合するかにおいて異なります。

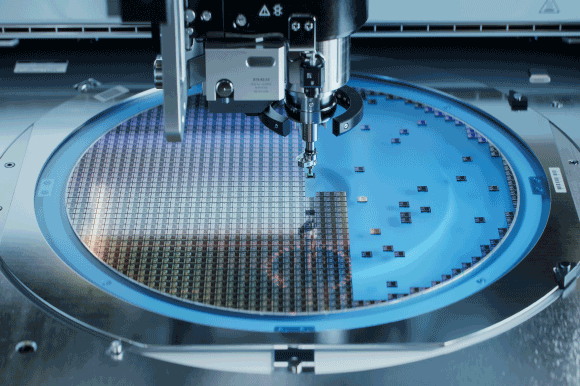

モノリシックCFET製造方法では、n型とp型のトランジスタが同時に、または一連のプロセスステップを通じて同一の半導体基板上に統合されます。シークエンシャルCFET製造方法では、n型とp型のトランジスタを別基板上に生成し、貼り合わせ接合することで、デバイスを生成します。

モノリシックでの製造はシークエンシャルに比べて製造コストが低いメリットがありますが、縦方向に積層していくために製造が難しいデメリットがあります。

一方で、シークエンシャルは別基板同士を張り合わせるため、製造プロセスが比較的簡素であるというメリットがありますが、1つのデバイスをつくるのに2枚のウェーハが必要となるためコストが高くなるというデメリットがあります。

上記のようにCFETは量産に向けて、製造方法含めてさらなる研究開発が必要ですが、従来のトランジスタの構造とはことなる点を生かして、半導体デバイスの進化とムーアの法則の継続に貢献する重要な技術革新を期待されています。

半導体製造現場の課題を解決!厳選ホワイトペーパー

半導体製造現場の「検査」「監視・調査」「セキュリティ」について、例を挙げて解説しています。日々の業務に是非ご活用ください。

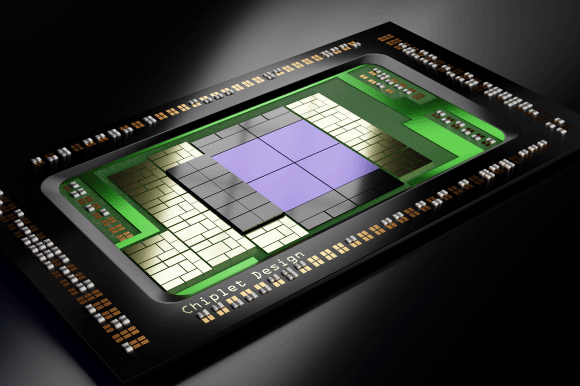

半導体は次の次元へ 微細化から集積へ アドバンストパッケージの世界

【この資料で分かること】

- 市場と技術の未来

- アドバンストパッケージの進化

- ウェーハ加工の課題解決

【こんな方におすすめ】

半導体市場やアドバンストパッケージ技術の動向を把握したい方、製造工程やウェーハ加工における課題解決を求めている方、高速化・高密度化を実現する製造技術に興味がある方、次世代半導体の開発に関わる技術者やエンジニアの方

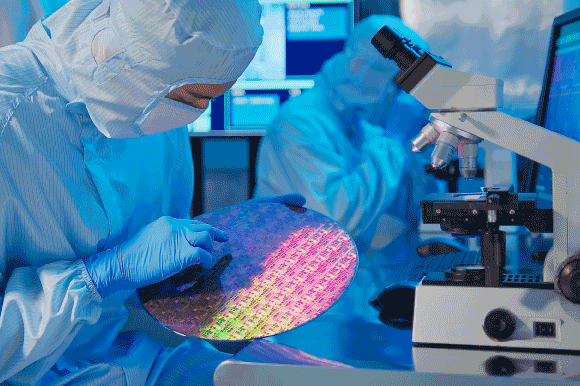

半導体ウェーハの外観検査まるわかりブック

【この資料で分かること】

- 多様なウェーハ材料

- ウェーハ製造工程と外観検査

- 欠陥の種類

- 検査技術のカテゴリ

【こんな方におすすめ】

Siウェーハ、化合物ウェーハ(SiC, GaN, LT/LN, InP), ガラスウェーハ等の検査に関心や課題をお持ちの方

半導体工場の現場DXガイドブック -設備の予知保全、品質監視-

【この資料で分かること】

- 半導体製造工程とDXの取組み

- 製造プロセス監視の作業自動化

- ウェーハ欠陥の原因調査

- 設備稼働監視作業の自動化

- 装置・設備・部品の故障予兆監視

【こんな方におすすめ】

ウェーハ製造工場や、デバイス製造工場のファシリティ設備の業務課題に関心や課題をお持ちの方

OTを止めるな!!半導体業界に必須のサイバー攻撃対策

【この資料で分かること】

- 外部脅威を排除しセキュアな工場へ

- 内部関係者によるリスク対策

- サプライチェーンリスク

- 横感染

- リスク発生&対策ソリューションマップ

【こんな方におすすめ】

半導体製造工場の現場、IT担当者、半導体装置メーカーでセキュリティに関心と課題をお持ちの方

- *¹ GAA(Gate all around)

- GAA(Gate-All-Around)トランジスタは、半導体トランジスタの設計方式の一つでゲートが半導体チャネルを全面的に囲む構造となっており、高い集積度、低電力消費、高性能を実現します。

- *² PMOS/NMOS

- PMOS(P型金属酸化物半導体)とNMOS(N型金属酸化物半導体)は、トランジスタの二つの基本的構造で、1対でCMOSトランジスタを構成します。PMOSはP型半導体を使用し、正の電圧でオフになる特性があります。対照的に、NMOSはN型半導体を使用し、負の電圧でオフになります。

- *³ PN距離

- pチャンネルとnチャンネルのトランジスタを分離するための距離のことです。